# **Table of Contents**

| The Programmable Gate Array                                       | _     |

|-------------------------------------------------------------------|-------|

| Introduction to Programmable Gate Arrays                          |       |

| Logic Cell Array Data Sheet XC2064 / XC2018                       |       |

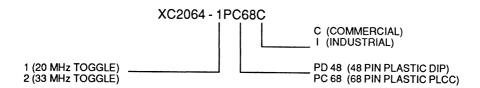

| Logic Cell Array Data Sheet XC2064-1 / XC2064-2                   |       |

| Testing and Data Integrity                                        |       |

| Non Hermetic Package Reliability                                  | 1-67  |

| Using Programmable Gate Arrays                                    |       |

| Methods of Configuring the Logic Cell Array                       | 2-1   |

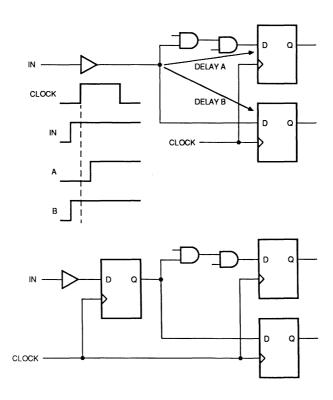

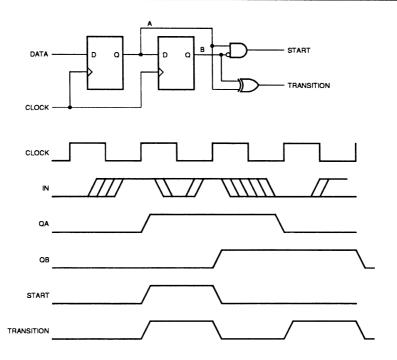

| Ins and Outs of Logic Cell Array I/O Blocks                       | 2-20  |

| Placement and Routing Optimization                                | 2-42  |

| A Design Methodology for the Logic Cell Array                     | 2-76  |

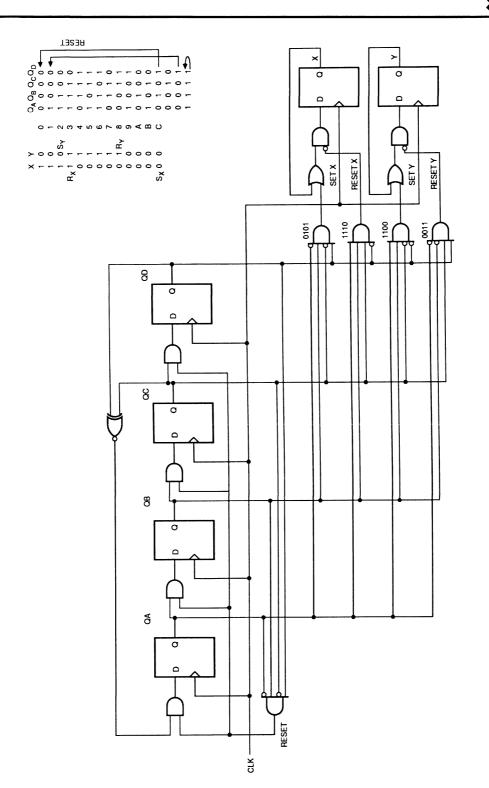

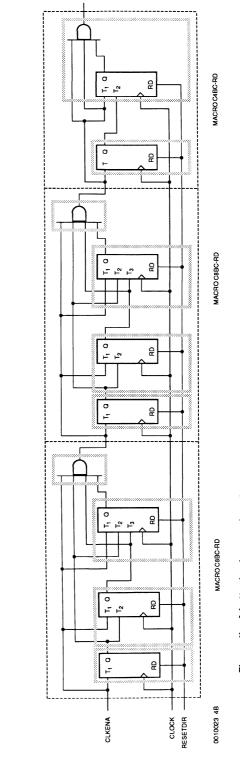

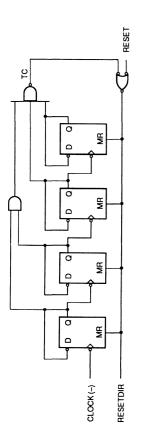

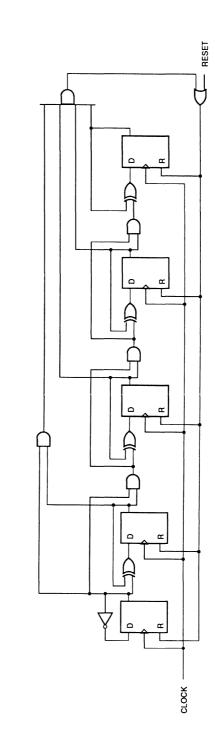

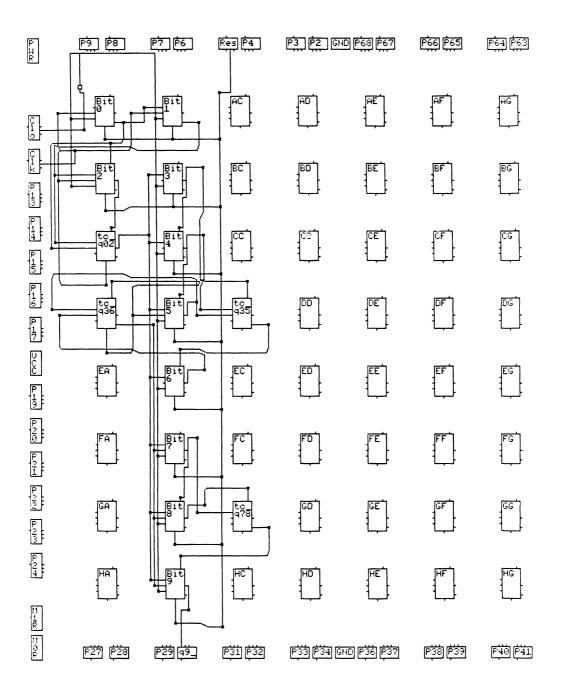

| Counter Examples                                                  | 2-98  |

| Metastability Analysis of Logic Cell Array Flip-flops             | 2-125 |

| Reading Back Logic Cell Array Configuration Programs              | 2-129 |

| Programmable Gate Array Design Examples                           |       |

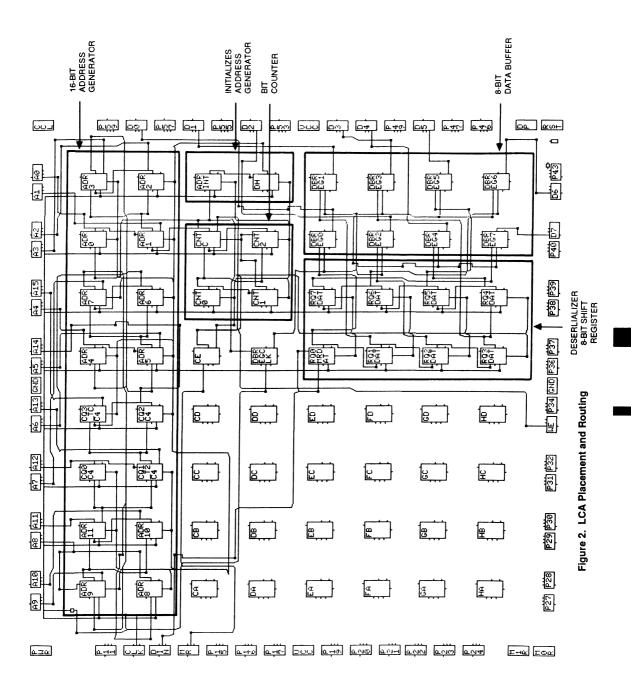

| A UART Design Example                                             | 3-1   |

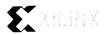

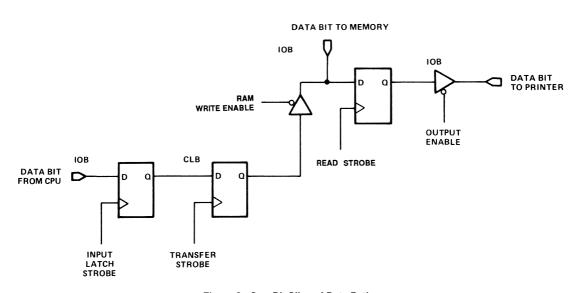

| A Printer Buffer Controller                                       | 3-11  |

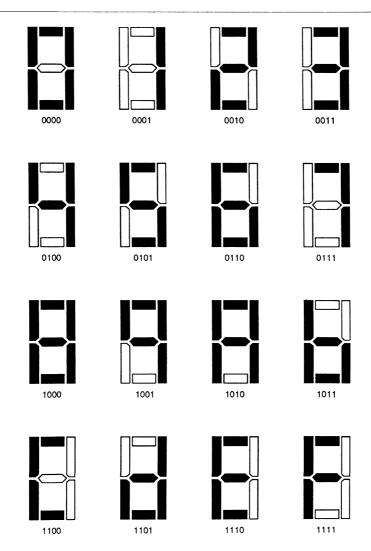

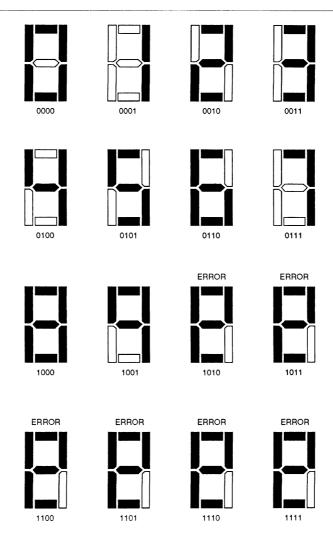

| A Seven Segment Display Driver                                    | 3-29  |

| Cost Effective Hardware/Software Updates                          | 3-41  |

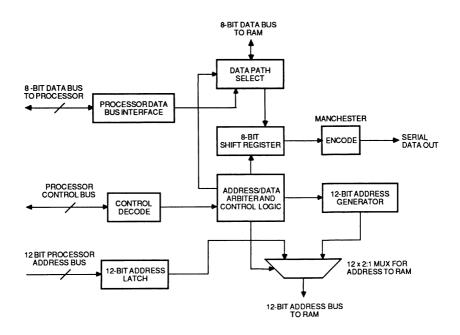

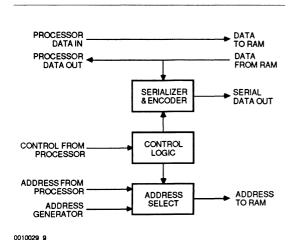

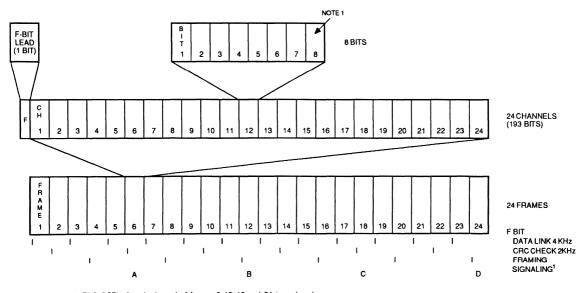

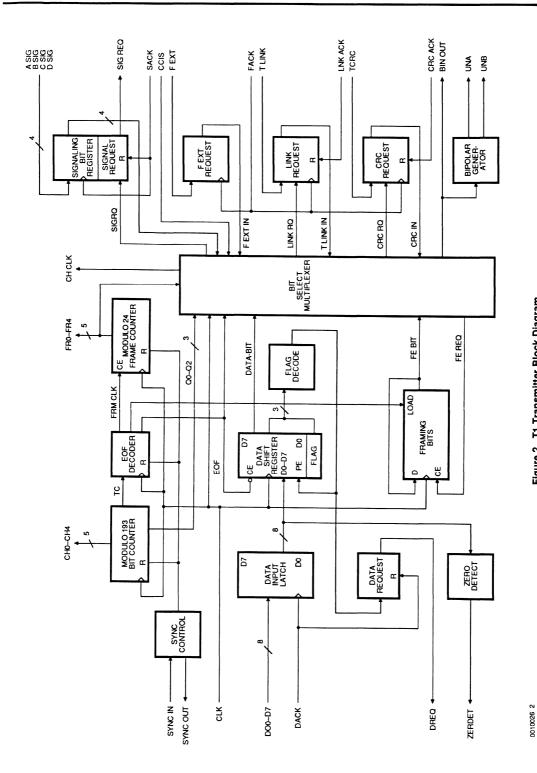

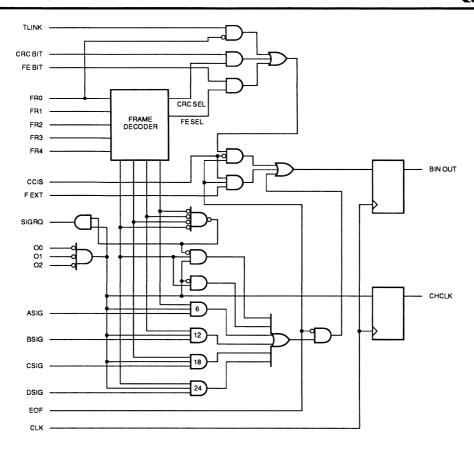

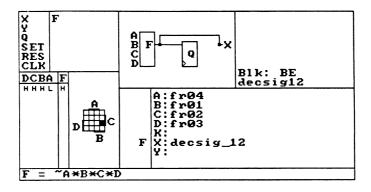

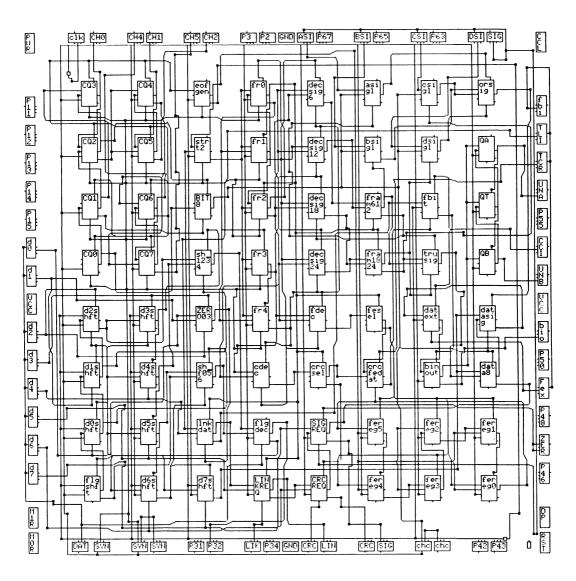

| A T1 Communications Interface                                     | 3-45  |

| Programmable Gate Array Development Systems                       |       |

| PC System Configurations                                          | 4-1   |

| In-Circuit Emulation and Simulation                               |       |

| Product Brief XC-DS21 XACT Design Editor                          | 4-19  |

| Product Brief XC-DS22 P-SILOS Simulator                           | 4-23  |

| Product Brief XC-DS23 Automated Placement and Routing             |       |

| Product Brief XC-DS24, 26, 27 XACTOR In-Circuit Emulator and Pods | 4-27  |

| Product Brief XC-DS31 FutureNet Schematic Library                 | 4-29  |

| Product Brief XC-EK01 Logic Cell Array Evaluation Kit             | 4-31  |

| Appendices                                                        |       |

| Technical References                                              | A-1   |

| Glossary                                                          | A-3   |

| Sales Offices List                                                | A-5   |

| Information Request Cards                                         |       |

#### Contributors

Chuck Erickson Steve Eliscu Rick Farabaugh Dave Galli Steve Knapp Steve Landry Dave Lautzenheiser Richard Ravel Rob Stransky Craig Wooster Pardner Wynn

© Copyright 1986 by Xilinx, Inc. All Rights Reserved.

# Patents Pending

Xilinx, Logic Cell, XACT, XACTOR and Logic Processor are trademarks of Xilinx, Inc. The Programmable Gate Array Company, is a Service Mark of Xilinx, Inc.

IBM is a registered trademark and PC, PC/AT, PC/XT are trademarks of International Business Machines Corporation. PAL is a registered trademark of Monolithic Memories, Inc. FutureNet is a registered trademark and DASH is a trademark of FutureNet Corporation, a Data I/O Company. SimuCad and Silos are registered trademarks and P-Silos is a trademark of SimuCad Corporation. MS-DOS is a trademark of Microsoft Corporation. LOGIMOUSE is a registered trademark of LOGITECH Inc. Lotus is a registered trademark of Lotus Development Corporation. AboveBoard and AboveBoard/PS are trademarks of Intel Corporation. RAMpage!, SixPakPlus and SixPakPremuim are registered trademarks of AST Research, Inc. Mouse Systems is a trademark of Mouse Systems Corporation. Microsoft is a registered trademark of Microsoft Corporation. Centronics is a registered trademark of Centronics Data Computer Corporation.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described herein; nor does it convey any license under its patent, copyright or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. cannot assume responsibility for the use of any circuitry described other than circuitry entirely embodied in their product. No other circuit patent licenses are implied.

Xilinx, Inc. cannot assume responsibility for any circuits shown or represent that they are free from patent infringement or of any other third party right.

Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made.

Printed in U.S.A.

# About the Company...

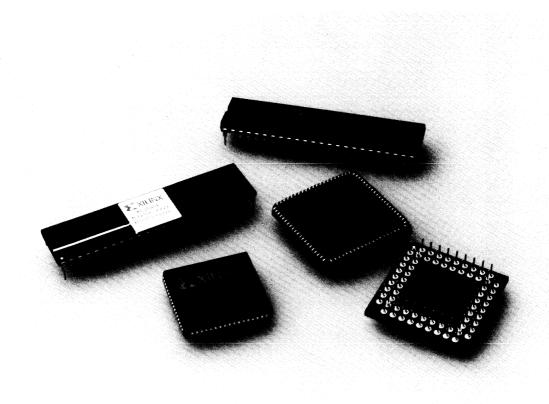

Xilinx was founded in February 1984 to develop a family of CMOS user-programmable gate arrays and associated development systems. The development of a general-purpose user-programmable logic device with an array architecture was the result of a number of technical breakthroughs, many of which have resulted in patent applications.

Due to its density and to the convenience of user programmability, the Logic Cell™ Array represents an important new alternative in the ASIC market. The company continues to concentrate its resources exclusively on expanding its growing family of Logic Processors™ and associated development systems.

# **Table of Contents**

|            | The Programmable Gate Array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|            | Introduction to Programmable Gate Arrays 1-1 Logic Cell Array Data Sheet XC2064 / XC2018 1-8 Logic Cell Array Data Sheet XC2064-1 / XC2064-2 1-50 Testing and Data Integrity 1-61 Non Hermetic Package Reliability 1-67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| i desar de |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|            | Methods of Configuring the Logic Cell Array2-1Ins and Outs of Logic Cell Array I/O Blocks2-20Placement and Routing Optimization2-42A Design Methodology for the Logic Cell Array2-76Counter Examples2-98Metastability Analysis of Logic Cell Array Flip-flops2-125Reading Back Logic Cell Array Configuration Programs2-129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|            | Manager and the state of the st |  |

|            | A UART Design Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| an a       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|            | PC System Configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|            | Technical References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

# Introduction to **Programmable Gate Arrays**

Requirements for improved product features, including lower cost, higher performance, reduced power consumption, smaller size and increased reliability are motivating manufacturers of electronic systems to use high-density VLSI circuits.

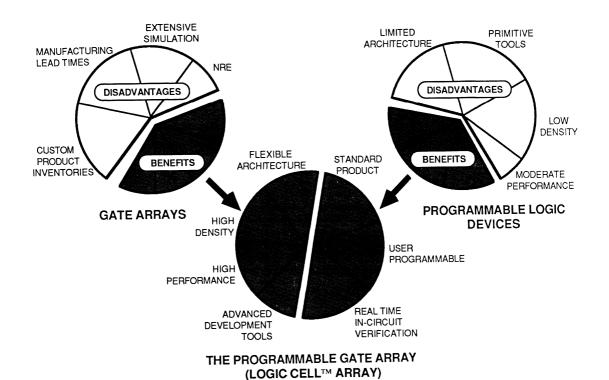

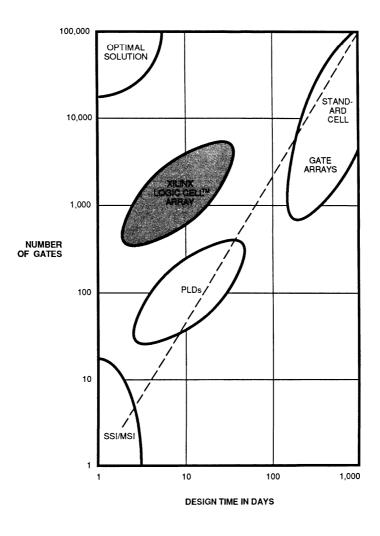

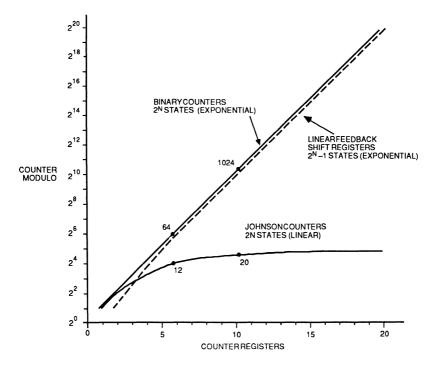

The standard product ICs that have best exploited advances in VLSI have been microprocessors and memories. Density improvements in these product families have outpaced other digital integrated circuits, widening the technology gap between them and other logic devices. To achieve comparable densities for their proprietary functions, designers of digital equipment have been forced to consider factory-programmed custom and semicustom application specific integrated circuits (ASICs). The advent of user-programmable gate arrays combines the production cost effectiveness of VLSI with all the benefits of a standard product. Figure 1 illustrates the tradeoffs of density and development time for several digital logic alternatives.

Standard SSI/MSI logic devices provide a great deal of flexibility, are well understood by most logic designers, and are readily available. However, they offer less density than other alternatives, and consume more power. These parts typically are manufactured in maturing technologies, with limited opportunity for further cost reductions.

The Programmable Logic Device (PLD) category includes a number of competing alternatives, all based on a programmable AND-OR plane architecture. The PLDs AND-OR plane architecture is most efficient for applications up to a few hundred usable gates. Bipolar PLDs are programmed by opening fuse links. CMOS PLDs can be one-time programmable, electrically programmabale (EPLDs), or electrically erasable (EEPLDs). These Programmable Logic Devices are often used in place of five to ten SSI/MSI devices. Since PLDs are user programmable, this gain in density can be achieved with only a small increase in design time and little schedule risk. Designs can be developed and devices programmed for a particular application in a matter of days. PLDs are best suited for state machines and decoders. Their architecture provides efficient multiple variable decoding and high performance for functions that are readily expressed as a sum-of-products. Architectural restrictions limit their application for general logic replacement, consolidation of miscellaneous "glue" and control functions, or complex processing tasks.

Factory programmable ASIC devices, including gate arrays, standard cells, and compiled silicon, provide logic densities up to 100,000 equivalent logic gates and are sufficiently flexible for most digital logic functions. After design completion and verification, factory programmed ASICs typically require two to four months for prototype fabrication and a similar period for the first production Because of their high design costs and quantities. limited production flexibility, factory-programmed ASICs are most economical in very high volume applications. The logistics of verifying a workable design, testing ICs and coordinating production demand require substantial and resources from the equipment manufacturer.

In the diagram, the upper left corner represents the best solution. The traditional tradeoffs between density and development time are illustrated by the dotted diagonal line in the diagram. As indicated, a new digital logic technology, the Logic Cell™ Array (LCA), offers improvements in both dimensions. This user-programmable gate array provides the system designer the usable density of gate arrays and the short development times and low risk of standard logic circuits. It combines the design and production benefits of a standard product with the system benefits of reliability, power savings, space savings, and lower production costs of ASIC devices.

# ARCHITECTURE

The user benefits of the Logic Cell Array are derived from its general-purpose array architecture. This architecture is based on a number of technical breakthroughs, many of which have resulted in patent disclosures.

The Logic Cell Array architecture is similar to that of a gate array, with an interior matrix of logic blocks and a surrounding ring of I/O interface blocks. User-programmable interconnection resources are used to create logic networks from these elements. In the Logic Cell Array, the functions of the logic and I/O blocks and the routing of interconnect networks are defined by a configuration program stored in an internal memory. Unlike conventional gate arrays, the Logic Cell Array requires no custom factory fabrication. Each device is identical until programmed by the user. The configuration program is loaded automatically from an EPROM

0010027 1

Figure 1. Logic Technology Tradeoffs

or programmed by a processor whenever the device is powered up, or upon command while the system is operating. Since the configuration program can be copyrighted, designs that employ Logic Cell Arrays can be protected from unauthorized copying under the same legal precedents that have been used effectively to protect microprocessor-based systems.

#### PROGRAMMABLE LOGIC DEVICES

In PLD architectures, inputs to the AND/OR planes are driven directly by dedicated input pins of the device and some user-selectable input/output pins or feedback paths. Outputs are driven directly from sum-of-products logic outputs or from flip-flops. The primary limitations of this architecture are the rigidity of the AND/OR plane logic and its dedicated interconnections. Flip-flops are typically driven by a common clock and are closely associated with specific output pins. As a result, gate utilization seldom exceeds 15%. Consequently, the practical upper limit of usable gates appears to be a few hundred and the extension of this basic architecture to higher densities is limited. Performance of PLDs is fixed for each level of logic. Each path through the AND/OR plane exhibits the same delay, typically 25–45 ns.

# **GATE ARRAYS**

Array architectures provide flexible resources, both for I/O functions and logic structures. With a gate array, user logic is typically implemented by interconnecting twoinput NAND gates into more complex functions using mask-programmed metal segments. Factory processing implements the metal interconnections required for each user configuration. Generation of larger arrays can be accomplished through straightforward extensions of the I/O, logic building blocks, and interconnect resources, much like extending the capacity of a memory device. Gate arrays offer usable densities of 25,000 gates or more. Utilization factors of 80-90% are possible because of the flexibility and regularity of the architecture. Gate array performance is dependent on the placement and interconnection of the elements that make up a logic network. In a gate array characterized by 2 ns gate delays, frequently used functions may have a total delay of 15 ns or more because of the levels of gating and the interconnection required to implement them.

# LOGIC CELL ARRAY

Logic Cell Arrays share the gate array architecture's flexibility and ease of extension to higher densities. The function of the LCA's configurable logic blocks and I/O blocks and their interconnection are controlled by a configuration program stored in an on-chip memory.

Distributed memory cells are adjacent to the logic, I/O, or interconnect element they control. Interconnect resources exist in the channels between the rows and columns of logic blocks and between the logic blocks and the I/O blocks. Through straightforward extensions of the array architecture, the initial 1200 gate LCA has been extended to an 1800 gate version. Further extensions of the LCA architecture will increase the number of usable gates to over 8000.

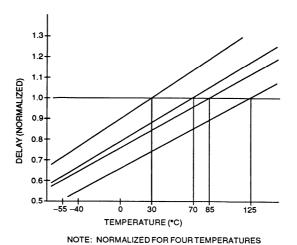

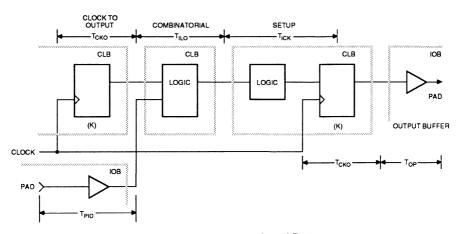

Like other standard IC components, Logic Cell Arrays permit the selection of higher speed parts from the natural distribution that results from the semiconductor manufacturing process. This permits the choice of the most cost-effective speed grade for a particular application. Logic Cell Array performance is determined by the fixed delays for logic and storage elements plus interconnect delays. During design, the timing calculation software in the development system can quickly display worst case timing. In general, Logic Cell Array performance is specified by the maximum toggle rate for a logic block storage element configured as a toggle flipflop. For typical configurations, a 70 MHz toggle rate translates to a system clock rate of up to 35 Mhz.

# **PROCESS**

Over the last five years, the most pronounced trend in semiconductor manufacturing processes has been the shift toward CMOS. This has been especially true for ASICs. The advantages of advanced CMOS processes include both high speed and low power consumption.

Logic Cell Arrays are fabricated through a partnership with Seiko-Epson, by means of an advanced twin-well, double-layer metal CMOS process. Two metal layers are essential for array architectures because of the need to propagate logic signals in both horizontal and vertical directions with minimum delays. The LCA manufacturing process is very similar to that used for high-speed memories. As a result it can exploit the photolithography and wafer diameter advances in memory process technology which result in ever higher density and performance at ever decreasing costs.

# QUALITY

As quality consciousness has grown among semiconductor users, awareness of the importance of testing has increased. Microprocessors, memories, and other standard products are designed for testability and are tested exhaustively with carefully developed test programs. The testing of most application specific ICs is less comprehensive, due to limitations of design and test program development. With respect to testing, the Logic Cell Array is like other standard products. It has been designed with 100% testability as a requirement and each device is comprehensively tested during the manufacturing process. This is accomplished without any participation by the user in the definition of test programs or the generation of test vectors.

#### RELIABILITY

The manufacturing process used for the Logic Cell Array is based on a process developed for high performance CMOS static memories. Extensive work on this process to insure the highest quality memory devices has provided the same benefits to the Logic Cell Array. Data collected over millions of Logic Cell Array device hours confirm the reliability of the design and the process. Compared with other logic devices, the Logic Cell Array exhibits extremely low power dissipation. This translates to lower operating temperatures and, correspondingly higher reliability. Packaging materials for the Logic Cell Array have been selected to match closely the thermal coefficient of expansion of the silicon. This minimizes thermal stresses and further improves reliability.

The memory cell used to store the LCA configuration program has been designed to be particularly robust. This memory is written only during device configuration and its static output controls logic elements in the array. Since the two circularly linked inverters that make up the static latch are adjacent, transients cause only minor differences in voltages. Each inverter is a true complementary transistor pair, so that a low impedance path to the supply rail always exists, regardless of state. In addition tests involving bombardment with high levels of alpha radiation verify that the storage cell is not disturbed by alpha particles.

# **DEVELOPMENT SYSTEMS**

The development system for the Logic Cell Array is similar in capabilities and usage to development systems for microprocessors.

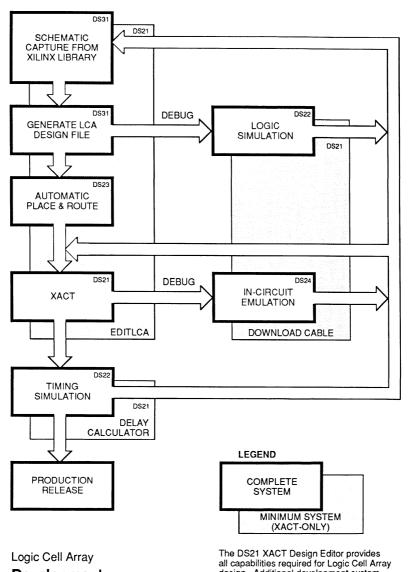

After the initial design information is entered into the XACT™ development system, it is checked for consistency and obvious errors. The design is then translated into a program for the LCA, which can be stored in EPROM devices or in some other media as needed by the final system. For debugging, the configuration is loaded into the LCA memory and in-circuit emulation is used to verify correct operation. Development system support for the Logic Cell Array includes complete facilities for design entry and design verification. The XACT development system includes a basic configuration and several options to enhance designer productivity. Features of the system include:

A consistent user-friendly environment under which all the development software and options are available

- Graphic driven design entry

- Schematic entry

- Interactive timing calculations

- Macro library support, both for standard Xilinx supplied functions and user-defined functions

- Design entry checking for consistency and completeness

- Automatic design documentation generation

- Automatic placement and routing

- Simulation interface support including netlist extraction

- Logic and timing simulation (P-SILOS™)

- In-circuit emulation for multiple devices

The XACT system operates on an IBM® PC/XT™, PC/AT™ or compatible system. Color graphics is required as well as 640 K bytes of internal RAM and a mouse. A full system also requires a single parallel port and two serial ports. Support for additional schematic editors and other design workstation platforms are being developed.

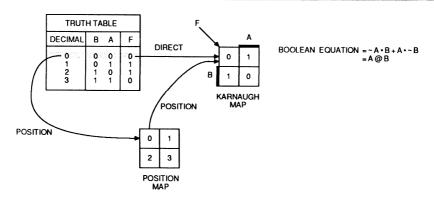

# Design Entry

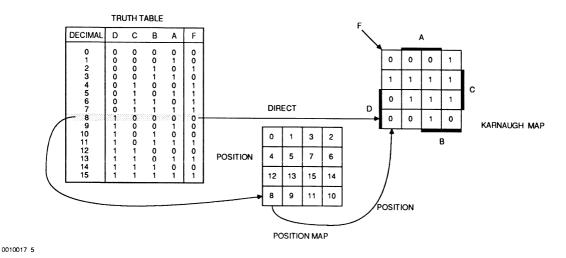

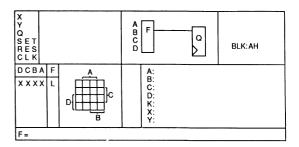

The first step in designing with the Logic Cell Array is to partition a design into logic blocks and I/O blocks, based on the capabilities of each of these resources. After partitioning, two alternatives are available for design entry. In the first, the XACT editor is used to enter the design directly. Design elements can be configured logic blocks and I/O blocks or system macros. The XACT editor allows the individual elements of either I/O or logic blocks to be configured directly, either through equations or Karnaugh maps. A macro can be selected to automatically configure a block or group of blocks for a specified function. Alternatively, the design can be entered in schematic form using the XACT design library with a supported schematic entry system.

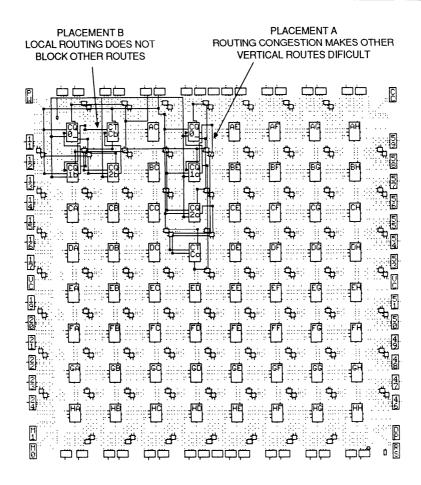

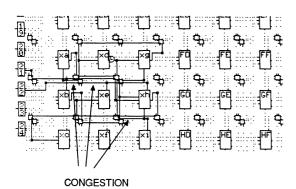

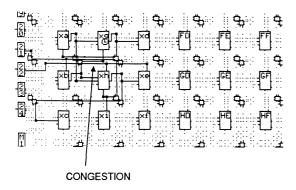

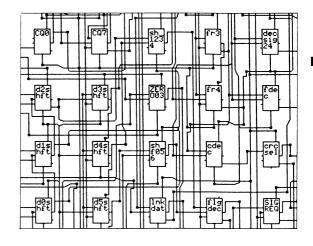

Placement and routing of the individual logic and I/O blocks may be performed interactively using the interconnect portion of the XACT editor. Alternatively, the optional Automatic Place and Route package can be used to place logic elements from a file created either by XACT or a schematic package and automatically route the logic networks. The output files produced by the schematic editor and by the auto place/route program are compatible with XACT, so that it can be used interactively for design optimization.

# Timing

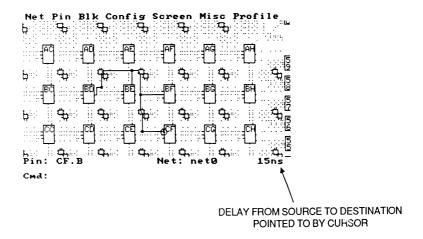

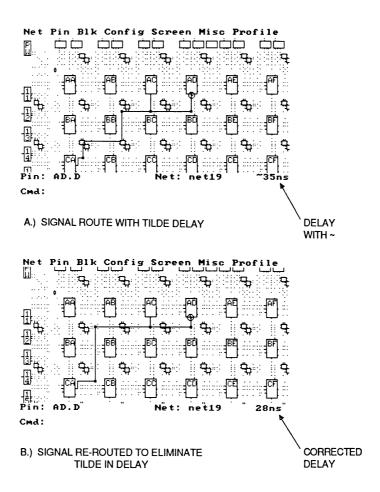

Timing for critical logic paths can be determined to check design performance. Delays associated with the routing of a particular signal path are displayed automatically. This represents the total worst-case delay from the

source block for that signal to the destination currently indicated by the mouse. In addition to displaying timing for individual networks, XACT can produce a listing showing timing for all logic networks in a design.

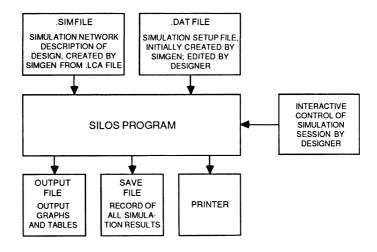

#### Simulation

After a design has been entered into XACT, a logic network can be extracted to create a netlist and timing model file for use with the optional P-SILOS logic and timing simulator. Because the XACT system automatically generates the logic description for the simulator, the user need only supply the input stimuli. Simulator output can be printed in a tabular format that shows the state of each selected node whenever any of the nodes changes. These data can be used to determine the relative timing of signals under worst-case conditions. The timing models from which the relative timing data are extracted are based on the implementation of the design and worst-case temperature, voltage and process conditions. Timing waveforms also can be generated automatically.

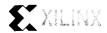

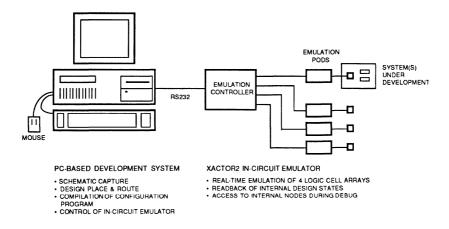

# In-Circuit Emulation

The ultimate verification of a design is its correct oper-

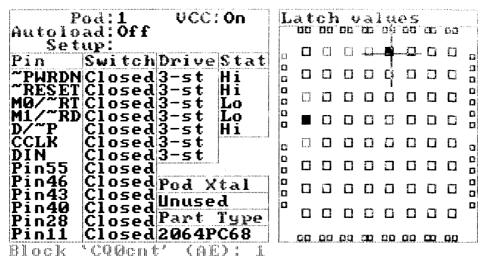

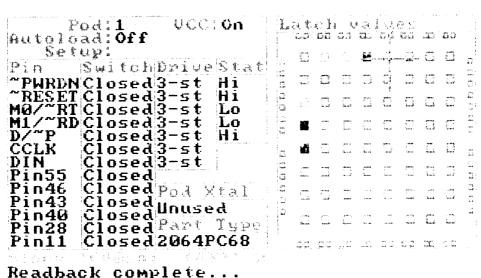

ation in the final system in which it will be used. This is the function of the optional XACTOR in-circuit emulator. Completed designs that have been converted into configuration programs are loaded directly into operating devices connected to the user's system. The system consists of software and hardware which is attached to the host PC system.

The XACTOR in-circuit emulator allows the user to emulate up to four devices simultaneously, with several design variations for each device. Emulation is accomplished by selectively isolating and controlling the pins of the Logic Cell Array which are associated with programming and overall device control. Isolation from the user's target system is accomplished with electronic switches controlled from the host system.

The emulator control software allows the user to program devices on command from either the development system or the target system. The system can also read and display the states of the internal logic block storage elements and I/O block inputs. Additional capabilities include reporting asynchronous events which occur in the target system and support for daisy chain programming of Logic Cell Arrays.

# XC2064 XC2018 Logic Cell™Array

# Table of Contents

| DESCRIPTION        | •     | •   |     |     | ٠  | • | • | • |  | • | ٠ | • | • | • | • | • | • |  |   | •  |   |  | 1-9  |

|--------------------|-------|-----|-----|-----|----|---|---|---|--|---|---|---|---|---|---|---|---|--|---|----|---|--|------|

| ARCHITECTURE       |       |     |     |     |    |   |   |   |  |   |   |   |   |   |   |   |   |  | • |    |   |  | 1-9  |

| Configuration Mem  | ory   | ,   |     |     |    |   |   |   |  |   |   |   |   |   |   |   |   |  |   |    |   |  | 1-9  |

| Input/Output Block | S.    |     |     |     |    |   |   |   |  |   |   |   |   |   |   |   |   |  |   |    |   |  | 1-10 |

| Configurable Logic | : Bl  | oc  | ks  |     |    |   |   |   |  |   |   |   |   |   |   |   |   |  |   |    |   |  | 1-11 |

| Interconnect       |       |     |     |     |    |   |   |   |  |   |   |   |   |   |   |   |   |  |   |    |   |  | 1-13 |

| Crystal Oscillator |       |     |     |     |    |   |   |   |  |   |   |   |   |   |   |   |   |  |   |    |   |  | 1-16 |

| POWER              |       |     |     |     |    |   |   |   |  |   |   |   |   |   |   |   |   |  |   |    |   |  | 1-18 |

| PROGRAMMING        |       |     |     |     |    |   |   |   |  |   |   |   |   |   |   |   |   |  |   |    |   |  | 1-20 |

| Initialization     |       |     |     |     |    |   |   |   |  |   |   |   |   |   |   |   |   |  |   |    | • |  | 1-20 |

| Programming        |       |     |     |     |    |   |   |   |  |   |   |   |   |   |   |   |   |  |   |    |   |  | 1-22 |

| Master Mode        |       |     |     |     |    |   |   |   |  |   |   |   |   |   |   |   |   |  |   |    |   |  | 1-22 |

| Peripheral Mode    |       |     |     |     |    |   |   |   |  |   |   |   |   |   |   |   |   |  |   |    |   |  | 1-23 |

| Slave mode         |       |     |     |     |    |   |   |   |  |   |   |   |   |   |   |   |   |  |   |    |   |  | 1-24 |

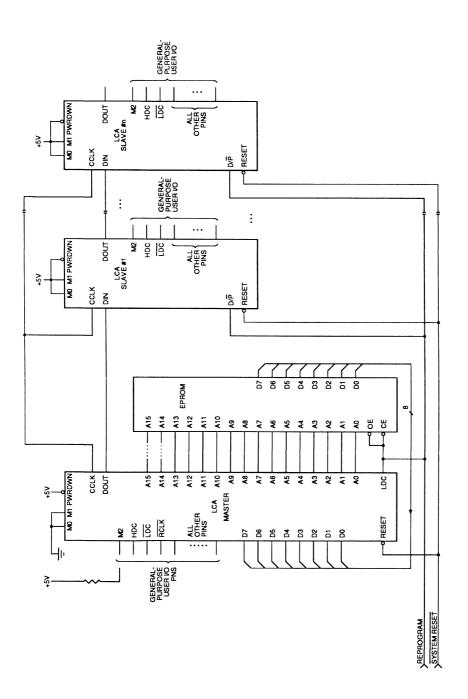

| Daisy Chain        |       |     |     |     |    |   |   |   |  |   |   |   |   |   |   |   |   |  |   |    |   |  | 1-24 |

| Operation          |       |     |     |     |    |   |   |   |  |   |   |   |   |   |   |   |   |  |   |    |   |  | 1-25 |

| Special Configurat | ion   | F   | und | cti | on |   |   |   |  |   |   |   |   |   |   |   |   |  |   | į. |   |  | 1-25 |

| Battery Backup     |       |     |     |     |    |   |   |   |  |   |   |   |   |   |   |   |   |  |   |    |   |  | 1-26 |

| PERFORMANCE        |       |     |     |     |    |   |   |   |  |   |   |   |   |   |   |   |   |  |   |    |   |  | 1-26 |

| Logic Block        |       |     |     |     |    |   |   |   |  |   |   |   |   |   |   |   |   |  | ٠ |    |   |  | 1-28 |

| Interconnect       |       |     |     |     |    |   |   |   |  |   |   |   |   |   |   |   |   |  |   |    |   |  | 1-28 |

| DEVELOPMENT SYST   | EM    | 1   |     |     |    |   |   |   |  |   |   |   |   |   |   |   |   |  |   |    |   |  | 1-30 |

| XACT General Fea   | ture  | es  |     |     |    |   |   |   |  |   |   |   |   |   |   |   |   |  |   |    |   |  | 1-30 |

| Designing with XA  | СТ    |     |     |     |    |   |   |   |  |   |   |   |   |   |   |   |   |  |   |    |   |  | 1-30 |

| MISCELLANEOUS      |       |     |     |     |    |   |   |   |  |   |   |   |   |   |   |   |   |  |   |    |   |  | 1-30 |

| Package Pin Desci  | ripti | ioi | าร  |     |    |   |   |   |  |   |   |   |   |   |   |   |   |  |   |    |   |  | 1-30 |

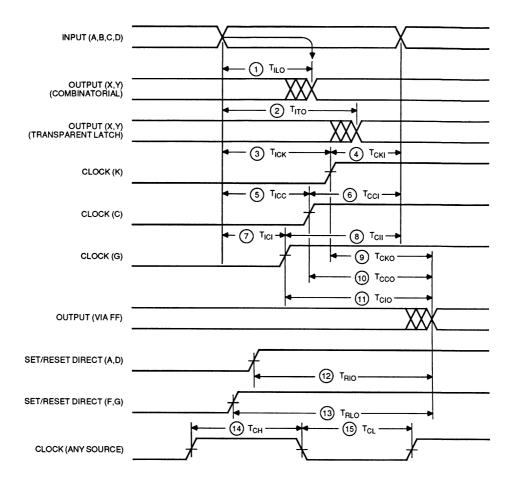

| Switching Charact  | eris  | sti | cs  |     |    |   |   |   |  |   |   |   |   |   |   |   |   |  |   |    |   |  | 1-38 |

| Ordering Informati | on    |     |     |     |    |   |   |   |  |   |   |   |   |   |   |   |   |  |   |    |   |  | 1-45 |

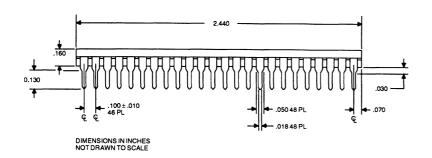

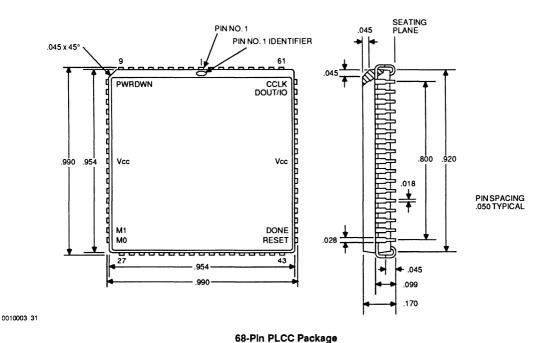

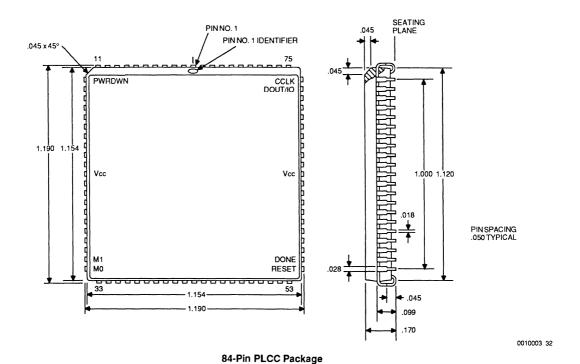

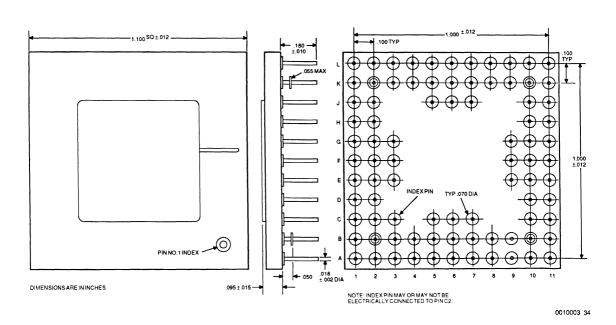

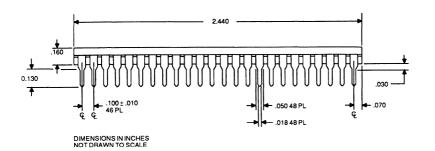

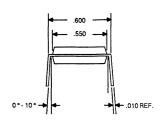

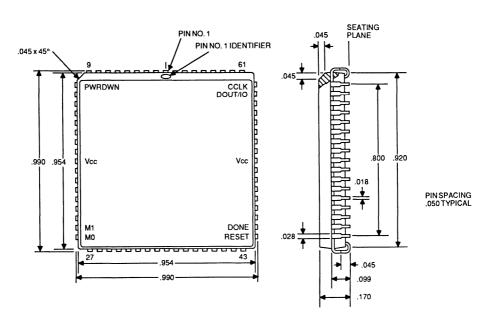

| Packages and Soc   | ket   | s   |     |     |    |   |   |   |  |   |   |   |   |   |   |   |   |  |   |    |   |  | 1-46 |

# XC2064 XC2018 Logic Cell™Array

# **Product Specification**

# **FEATURES**

- · Fully user-programmable:

- I/O functions

- · Digital logic functions

- Interconnections

- · General-purpose array architecture

- · Complete user control of design cycle

- Compatible arrays with logic cell complexity equivalent to 1200 and 1800 usable gates

- · Standard product availability

- 100% factory-tested

- · Selectable configuration modes

- · Low-power, CMOS, static memory technology

- · Performance equivalent to TTL SSI/MSI

- · TTL or CMOS input thresholds

- · Complete development system support

- · XACT Design Editor

- Schematic Entry

- XACTOR In Circuit Emulator

- · Macro Library

- · Timing Calculator

- · Logic and Timing Simulator

- Auto Place / Route

# DESCRIPTION

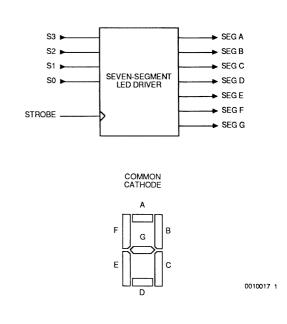

The Logic Cell™ Array (LCA) is a high density CMOS integrated circuit. Its user-programmable array architecture is made up of three types of configurable elements: Input/Output Blocks, Logic Blocks and Interconnect. The designer can define individual I/O blocks for interface to external circuitry, define logic blocks to implement logic functions and define interconnection networks to compose larger scale logic functions. The XACT™ Development System provides interactive graphic design capture and automatic routing. Both logic simulation and in-circuit emulation are available for design verification.

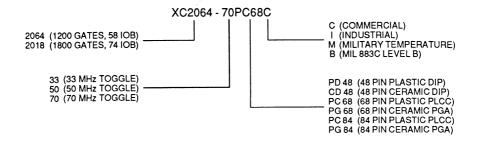

The Logic Cell Array is available in a variety of logic capacities, package styles, temperature ranges and speed grades.

| Part<br>Number | Logic<br>Capacity<br>(usable)<br>gates | Config-<br>urable<br>Logic<br>Blocks | User<br>I/Os | Configuration Program (bits) |

|----------------|----------------------------------------|--------------------------------------|--------------|------------------------------|

| XC2064         | 1200                                   | 64                                   | 58           | 12038                        |

| XC2018         | 1800                                   | 100                                  | 74           | 17878                        |

The Logic Cell Array's logic functions and interconnections are determined by data stored in internal static memory cells. On-chip logic provides for automatic loading of configuration data at power-up. The program data can reside in an EEPROM, EPROM or ROM on the circuit board or on a floppy disk or hard disk. The program can be loaded in a number of modes to accommodate various system requirements.

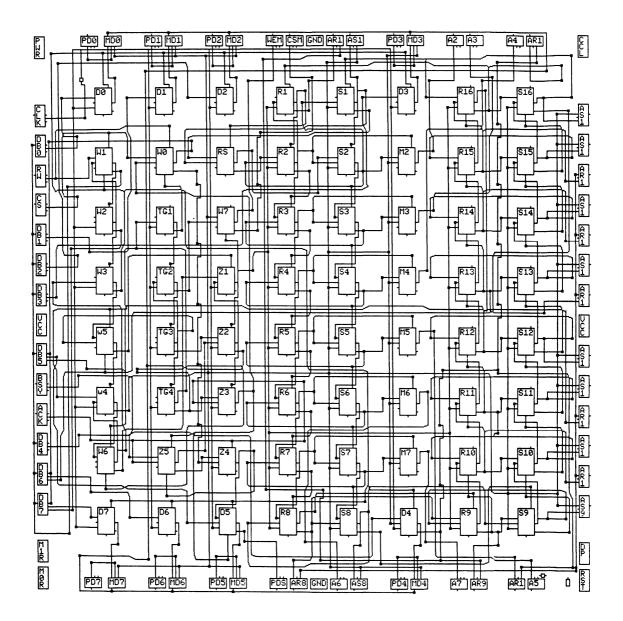

#### **ARCHITECTURE**

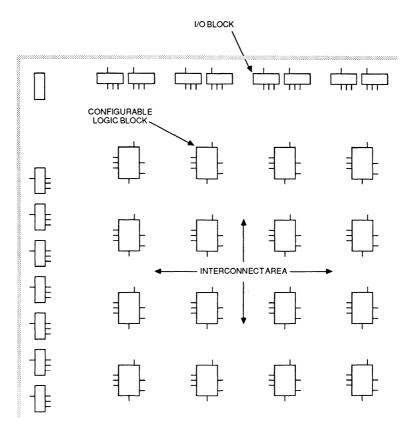

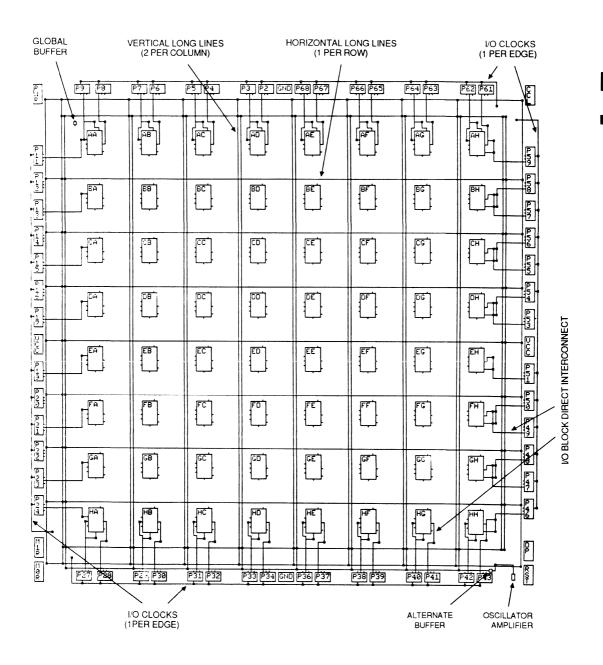

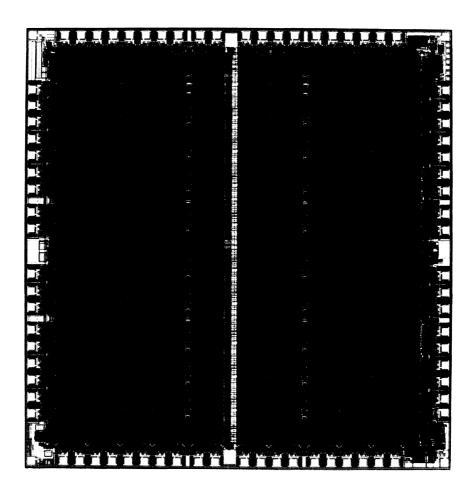

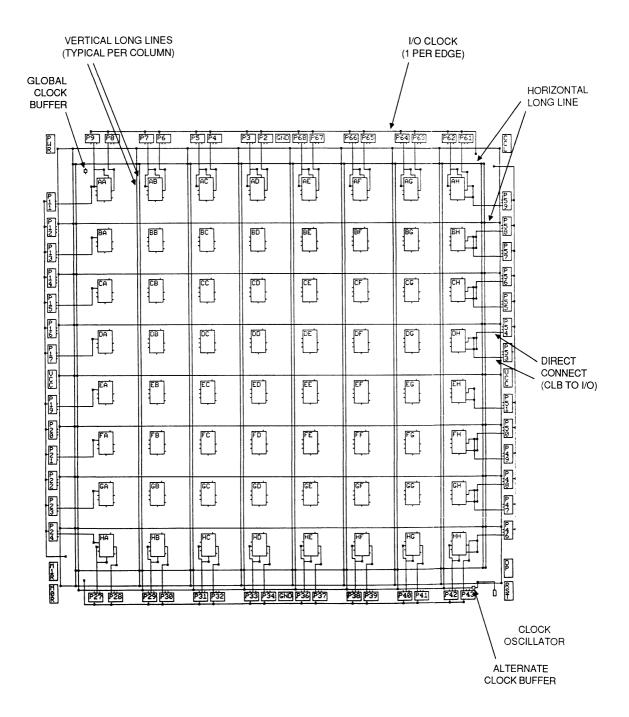

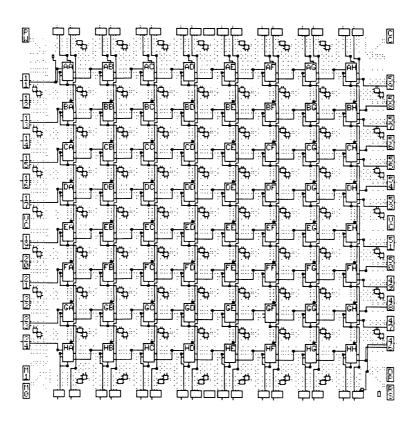

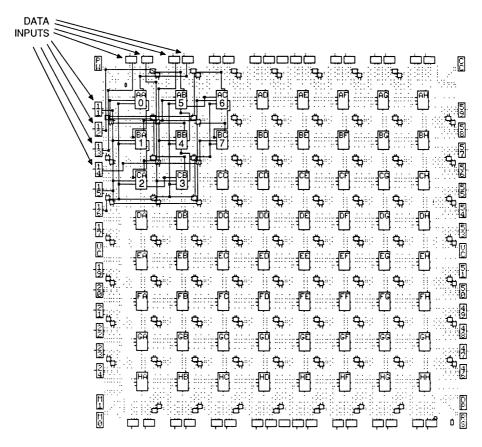

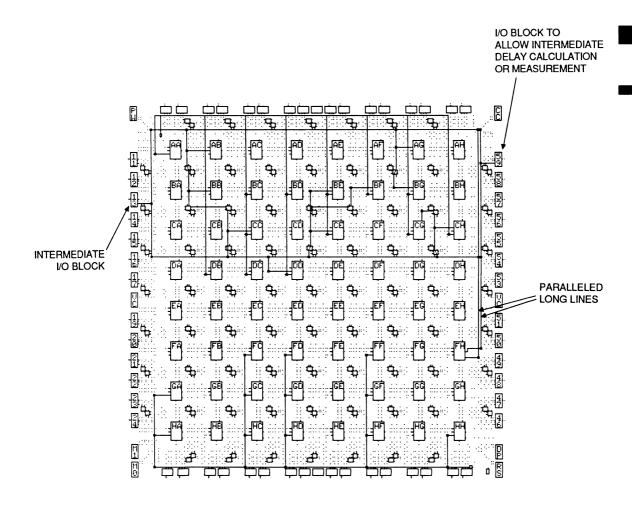

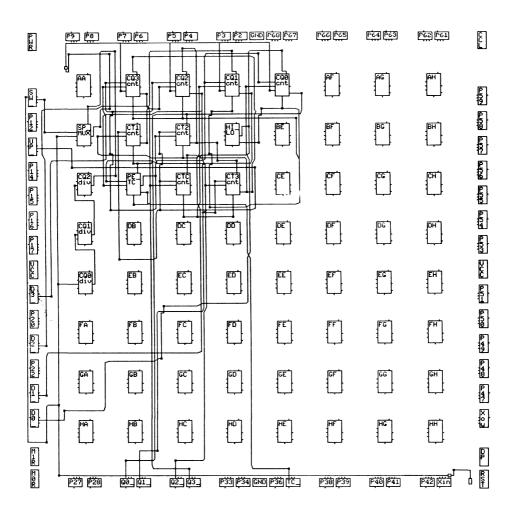

The general structure of a Logic Cell Array is shown in Figure 1. The elements of the array include three categories of user programmable elements: I/O Blocks, Configurable Logic Blocks and Programmable Interconnections. The I/O Blocks provide an interface between the logic array and the device package pins. The Configurable Logic Blocks perform user-specified logic functions, and the interconnect resources are programmed to form networks that carry logic signals among blocks.

Configuration of the Logic Cell Array is established through a distributed array of memory cells. The XACT development system generates the program used to configure the Logic Cell Array. The Logic Cell Array includes logic to implement automatic configuration.

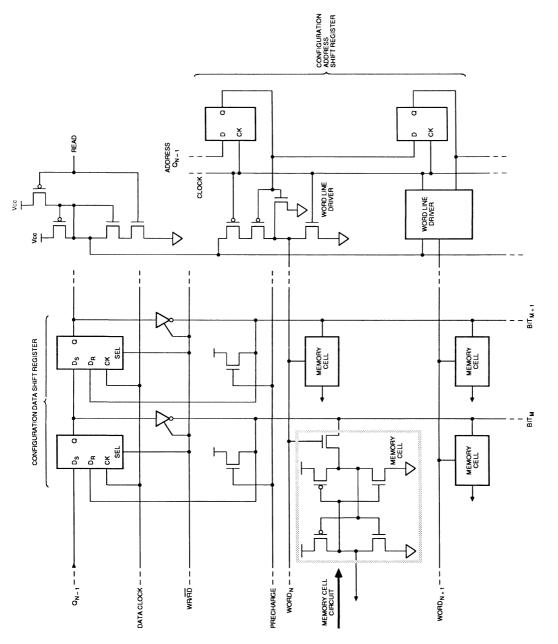

# Configuration Memory

The configuration of the Xilinx Logic Cell Array is established by programming memory cells which determine the logic functions and interconnections. The memory loading process is independent of the user logic functions.

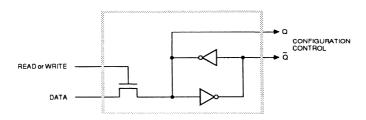

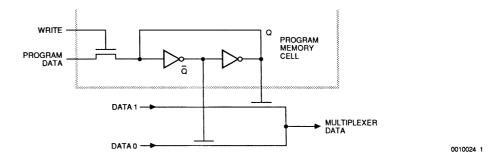

The static memory cell used for the configuration memory in the Logic Cell Array has been designed

specifically for high reliability and noise immunity. Based on this design, which is covered by a pending patent application, integrity of the LCA configuration memory is assured even under adverse conditions. Compared with other programming alternatives, static memory provides the best combination of high density, high performance, high reliability and comprehensive testability. As shown in Figure 2, the basic memory cell consists of two CMOS inverters plus a pass transistor used for writing data to the cell. The cell is only written during configuration and only read during readback. During normal operation the pass transistor is "off" and does not affect the stability of the cell. This is quite different from the normal operation of conventional memory devices, in which the cells are continuously read and rewritten.

The outputs Q and Q control pass-transistor gates directly. The absence of sense amplifiers and the output capacitive load provide additional stability to the cell. Due to the structure of the configuration memory

cells, they are not affected by extreme power supply excursions or very high levels of alpha particle radiation. In reliability testing no soft errors have been observed, even in the presence of very high doses of alpha radiation.

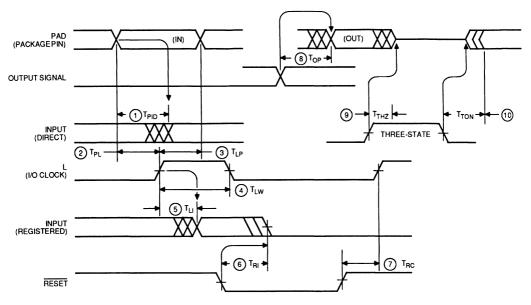

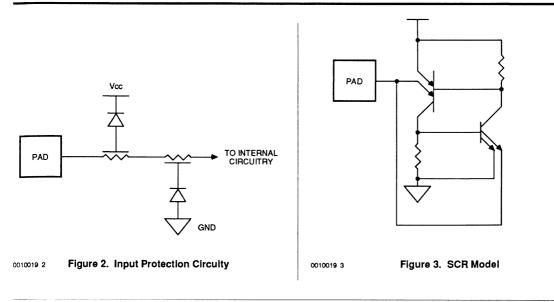

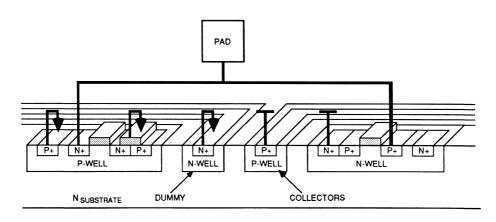

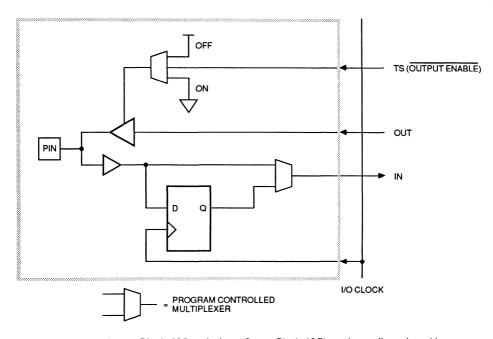

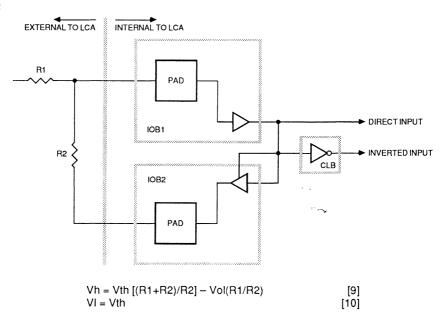

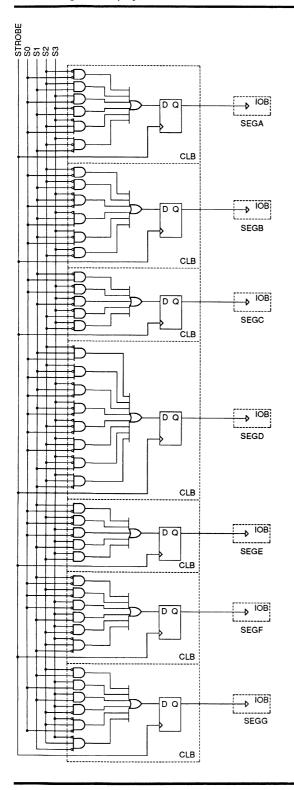

# Input/Output Block

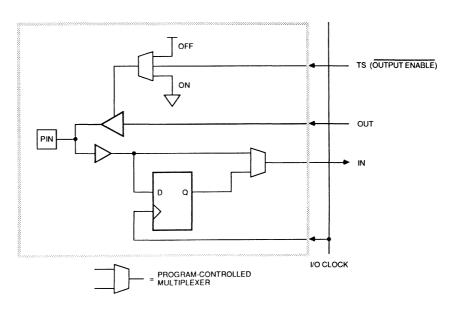

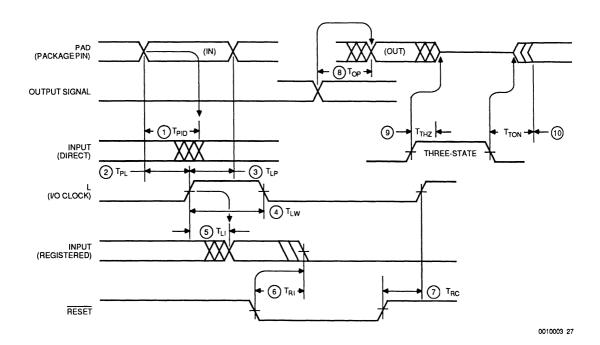

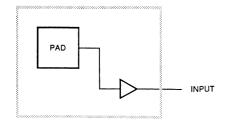

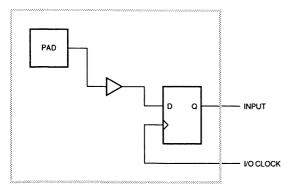

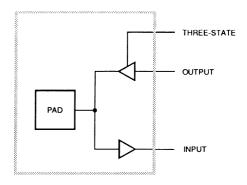

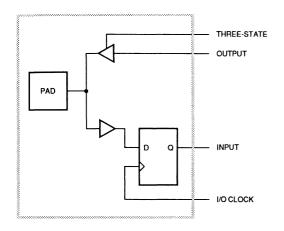

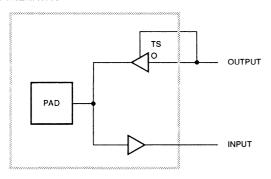

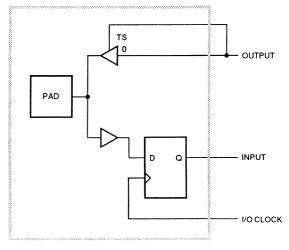

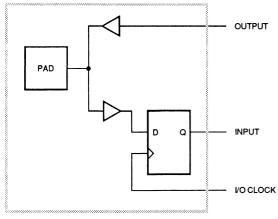

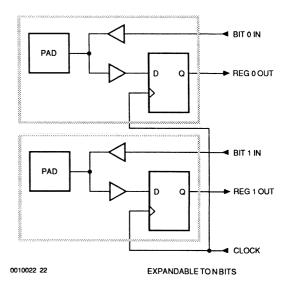

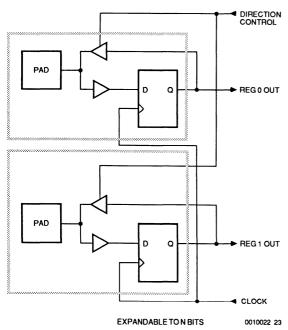

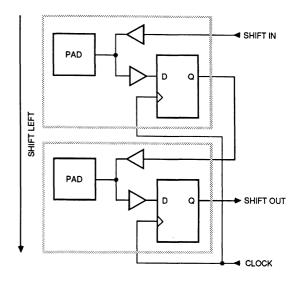

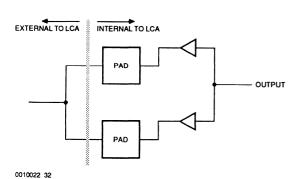

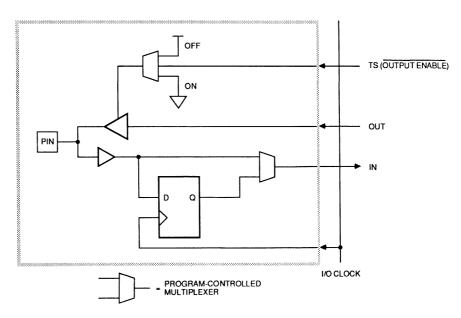

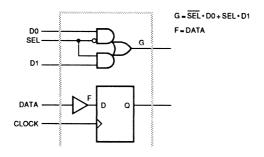

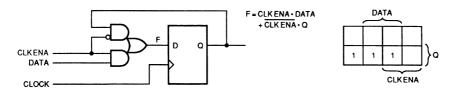

Each user-configurable I/O block (IOB) provides an interface between the external package pin of the device and the internal logic. Each I/O block includes a programmable input path and a programmable output buffer. It also provides input clamping diodes to provide protection from electro-static damage, and circuits to protect the LCA from latch-up due to input currents. Figure 3 shows the general structure of the I/O block.

The input buffer portion of each I/O block provides threshold detection to translate external signals applied to the package pin to internal logic levels. The input buffer threshold of the I/O blocks can be programmed to

Figure 1. Logic Cell Array Structure

0010003 1

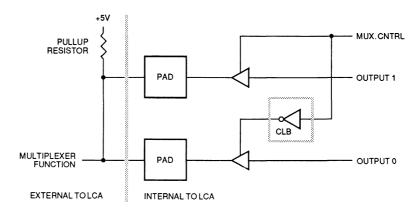

be compatible with either TTL (1.4 V) or CMOS (2.2 V) levels. The buffered input signal drives both the data input of an edge triggered D flip-flop and one input of a two-input multiplexer. The output of the flip-flop provides the other input to the multiplexer. The user can select either the direct input path or the registered input, based on the content of the memory cell controlling the multiplexer. The I/O Blocks along each edge of the die share common clocks. The flip-flops are reset during configuration as well as by the active-low chip RESET input.

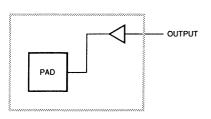

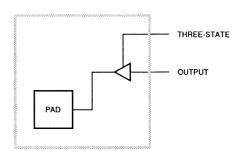

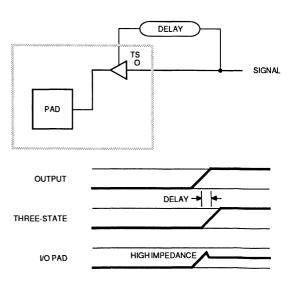

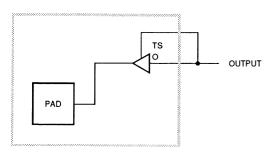

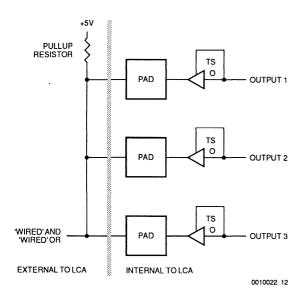

Output buffers in the I/O blocks provide 4 mA drive for high fan-out CMOS or TTL compatible signal levels. The output data (driving I/O block pin O) is the data source

for the I/O block output buffer. Each I/O block output buffer is controlled by the contents of two configuration memory cells which turn the buffer ON or OFF or select logical three-state buffer control. The user may also select the output buffer three-state control (I/O block pin TS). When this I/O block output control signal is HIGH (a logic "1") the buffer is disabled and the package pin is high-impedance.

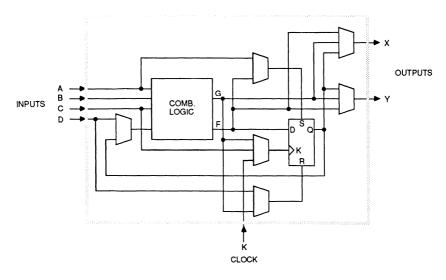

# Configurable Logic Block

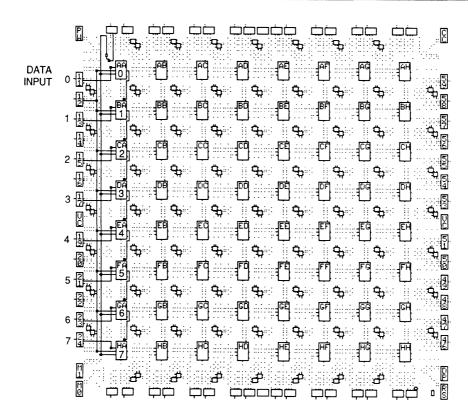

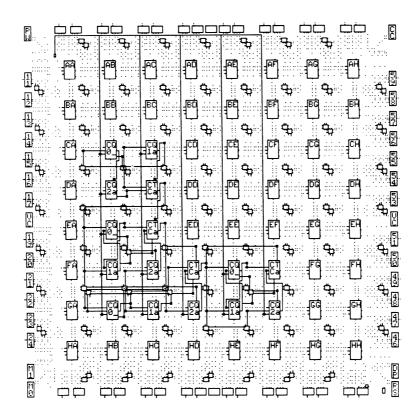

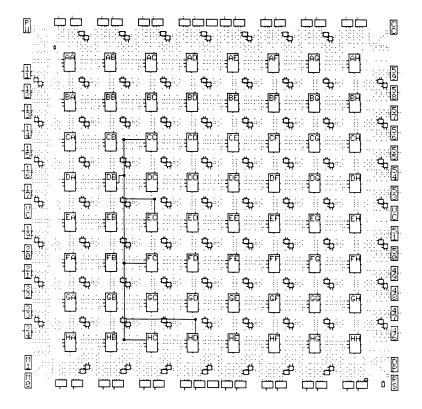

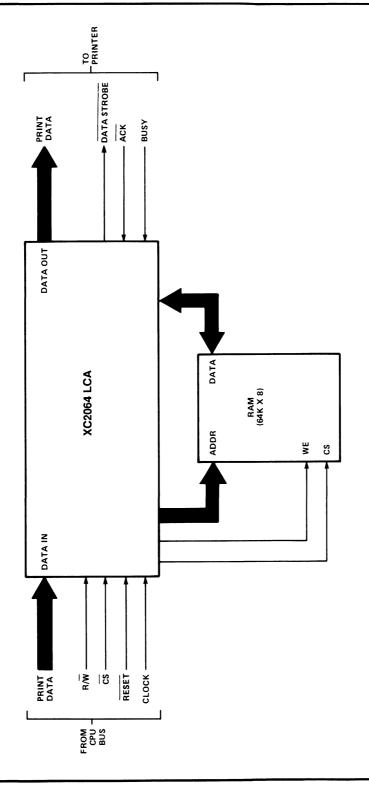

An array of Configurable Logic Blocks (CLBs) provides the functional elements from which the user's logic is constructed. The Logic Blocks are arranged in a matrix in the center of the device. The XC2064 has 64 such

0010003 2

Figure 2. Configuration Memory Cell

0010003 3

Figure 3. I/O Block

Figure 4. Configurable Logic Block

0010003 4

blocks arranged in an 8-row by 8-column matrix. The XC-2018 has 100 logic blocks arranged in a 10 by 10 matrix.

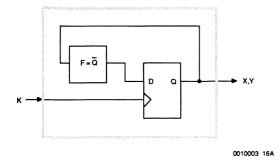

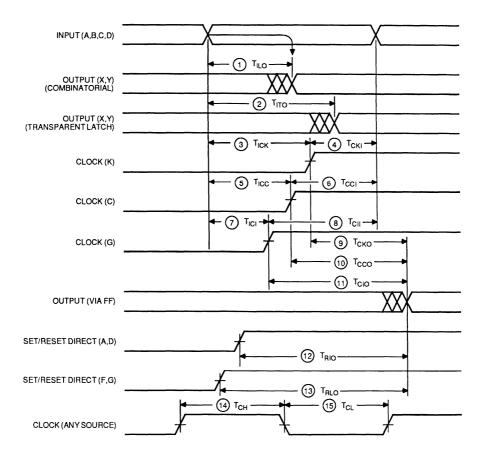

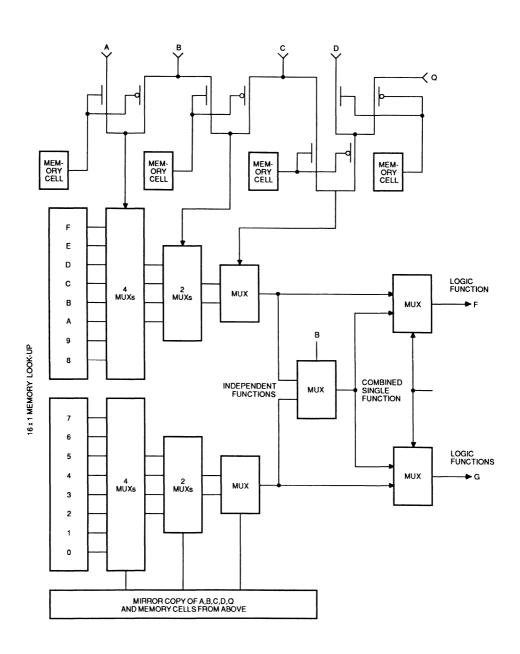

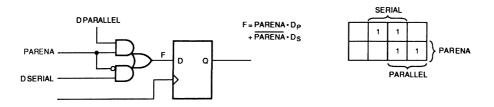

Each logic block has a combinatorial logic section, a storage element, and an internal routing and control section. Each CLB has four general-purpose inputs: A, B, C and D; and a special clock input (K), which may be driven from the interconnect adjacent to the block. Each CLB also has two outputs, X and Y, which may drive interconnect networks. Figure 4 shows the resources of a Configurable Logic Block.

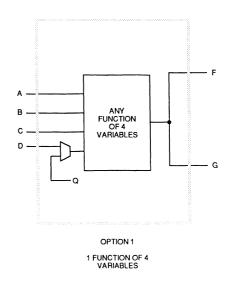

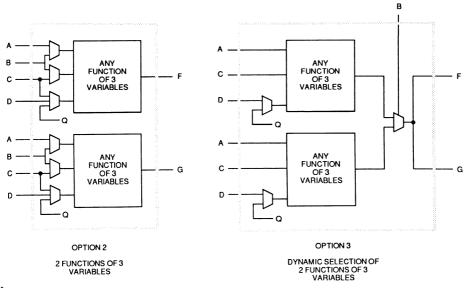

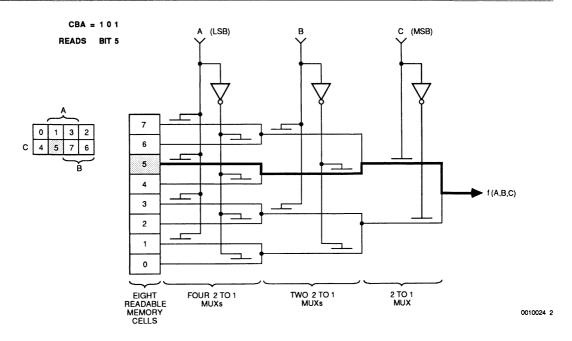

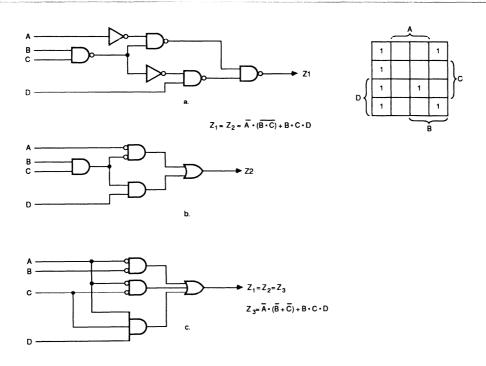

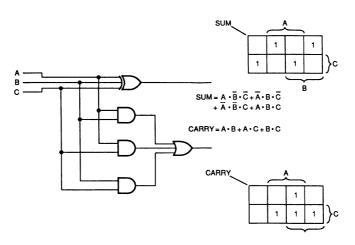

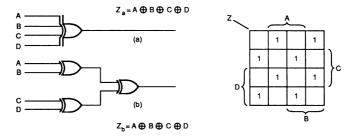

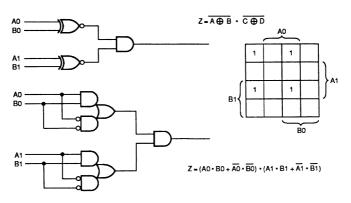

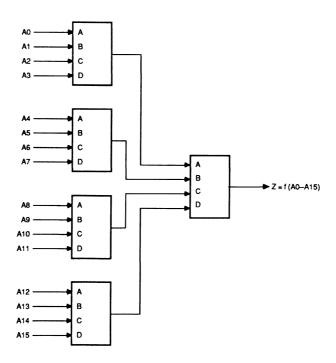

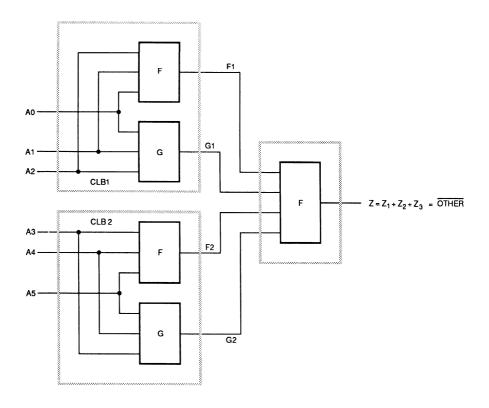

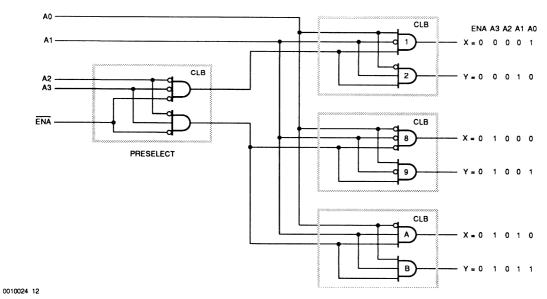

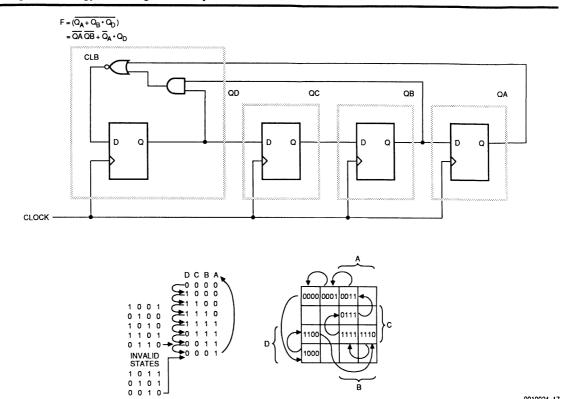

The logic block combinatorial logic uses a table look-up memory to implement Boolean functions. This technique can generate any logic function of up to four variables with a high speed sixteen-bit memory. The propagation delay through the combinatorial network is independent of the function generated. Each block can perform any function of four variables or any two functions of three variables each. The variables may be selected from among the four inputs and the block's storage element output "Q". Figure 5 shows various options which may be specified for the combinatorial logic.

If the single four-variable configuration is selected (Option 1), the F and G outputs are identical. If the two-function alternative is selected (Option 2), logic functions F and G may be independent functions of three variables each. The three variables can be selected from among the four logic block inputs and its storage element output "Q". A third form of the combi-

natorial logic (Option 3) is a special case of the twofunction form in which the B input dynamically selects between the two function tables providing a single merged logic function output. This dynamic selection

allows some five-variable functions to be generated from the four block inputs and storage element Q. Combinatorial functions are restricted in that one may not use both its storage element output Q and the input variable of the logic block pin "D" in the same function.

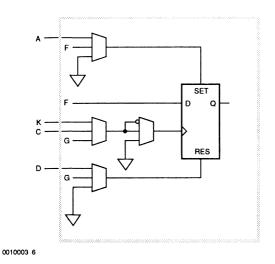

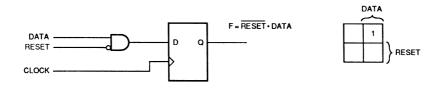

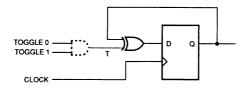

If used, the storage element in each Configurable Logic Block (Figure 6) can be programmed to be either an edge-sensitive "D" type flip-flop or a level-sensitive "D" latch. The clock or enable for each storage element can be selected from:

- · The special-purpose clock input K

- · The general-purpose input C

- The combinatorial function G

The user may also select the clock active sense within each logic block. This programmable inversion eliminates the need to route both phases of a clock signal throughout the device.

The storage element data input is supplied from the function F output of the combinatorial logic. Asynchronous SET and RESET controls are provided for each storage element. The user may enable these controls independently and select their source. They are active

high inputs and the asynchronous reset is dominant. The storage elements are reset by the active-low chip RESET pin as well as by the initialization phase preceding configuration. If the storage element is not used, it is disabled.

The two block outputs, X and Y, can be driven by either the combinatorial functions, F or G, or the storage element output Q (Figure 4). Selection of the outputs is completely interchangeable and may be made to optimize routing efficiencies of the networks interconnecting the logic blocks and I/O blocks.

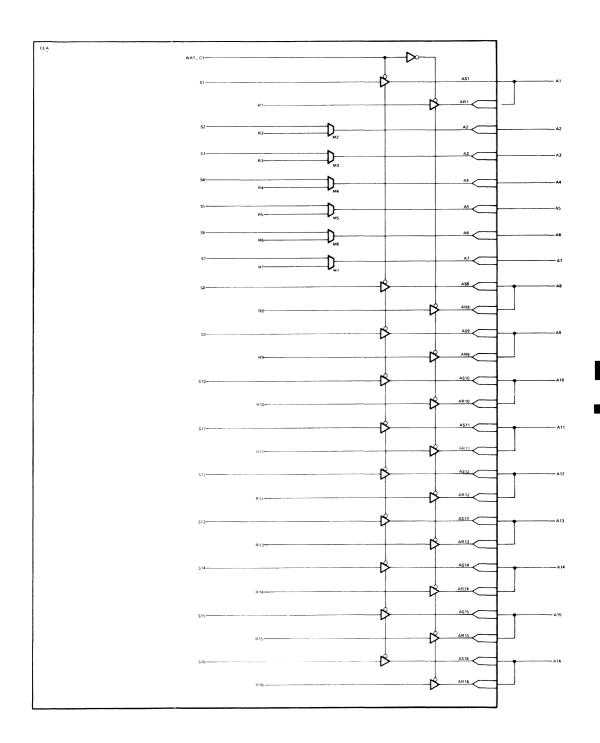

# Programmable Interconnect

Programmable interconnection resources in the Logic Cell Array provide routing paths to connect inputs and outputs of the I/O and logic blocks into desired networks. All interconnections are composed of metal segments, with programmable switching points provided to implement the necessary routing. Three types of resources accommodate different types of networks:

- General purpose interconnect

- · Long lines

- · Direct connection

0010003 5

Figure 5. CLB Combinatorial Logic Options

#### General-Purpose Interconnect

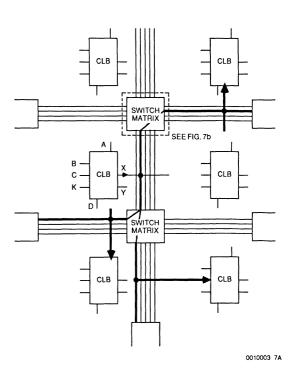

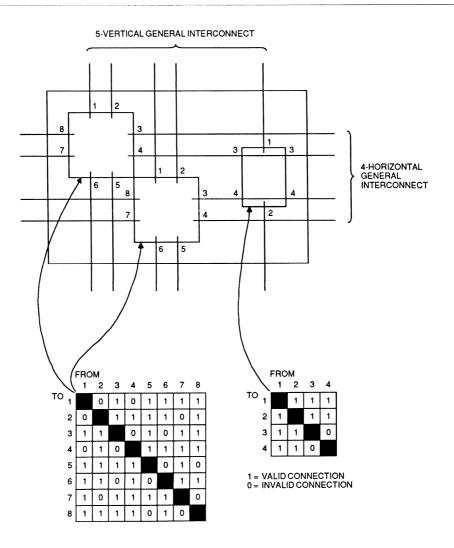

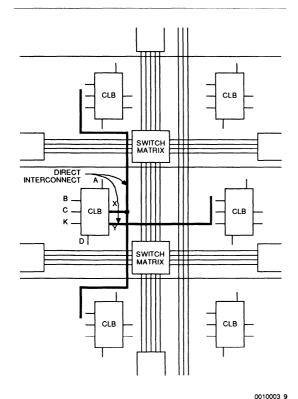

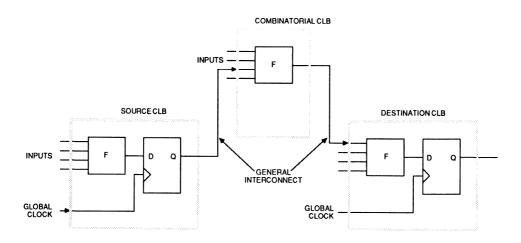

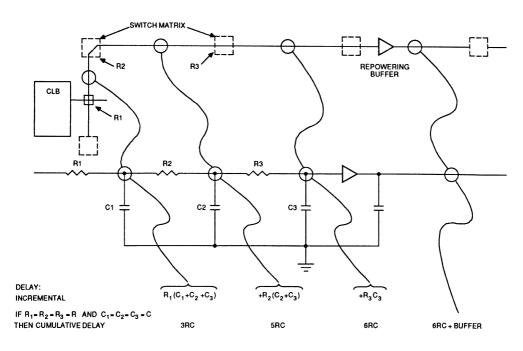

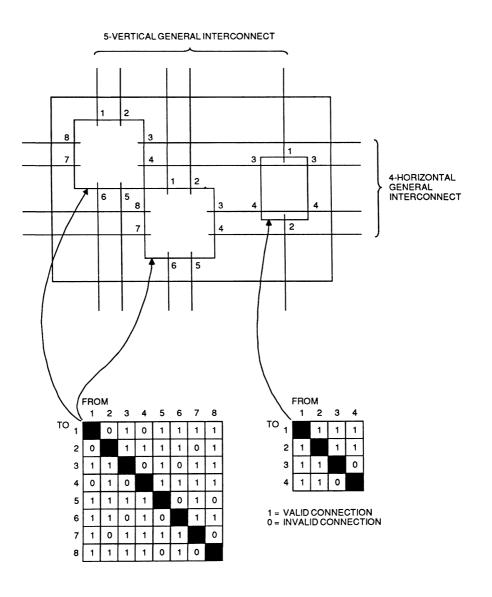

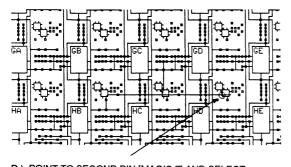

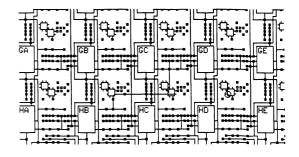

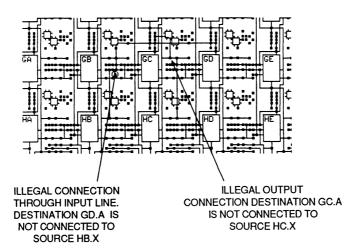

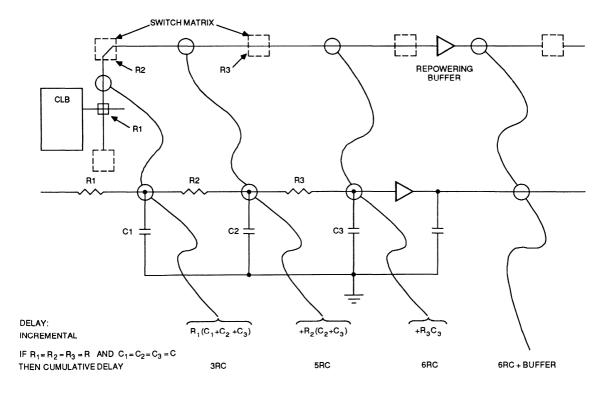

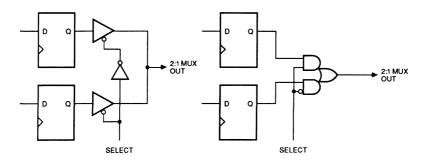

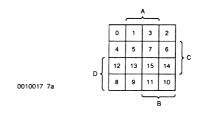

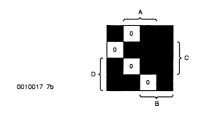

General-purpose interconnect, as shown in Figure 7a, is composed of four horizontal metal segments between the rows and five vertical metal segments between the columns of logic and I/O blocks. Each segment is only the "height" or "width" of a logic block. Where these segments would cross at the intersections of rows and columns, switching matrices are provided to allow interconnections of metal segments from the adjoining rows and columns. Switches in the switch matrices and on block outputs are specially designed transistors, each controlled by a configuration bit.

Logic block output switches provide contacts to adjacent general interconnect segments and therefore to the switching matrix at each end of those segments. A switch matrix can connect an interconnect segment to other segments to form a network. Figure 7a shows the general interconnect used to route a signal from one logic block to three other logic blocks. As shown, combinations of closed switches in a switch matrix allow multiple branches for each network. The inputs of the logic or I/O blocks are multiplexers that can be programmed with configuration bits to select an input network from the adjacent interconnect segments. Since the switch connections to block inputs are unidirectional (as are block outputs) they are usable only for input connection. The development system software provides automatic routing of these interconnections. Interactive routing is also available for design optimization. This is accomplished by selecting a network and then toggling

A F SET D O RES

Figure 6. CLB Storage Elememt

the states of the interconnect points by selecting them with the "mouse". In this mode, the connections through the switch matrix may be established by selecting pairs of matrix pins. The switching matrix combinations are indicated in Figure 7b.

Special buffers within the interconnect area provide periodic signal isolation and restoration for higher general interconnect fan-out and better performance. The repowering buffers are bidirectional, since signals must be able to propagate in either direction on a general interconnect segment. Direction controls are automatically established by the Logic Cell Array development system software. Repowering buffers are provided only for the general-purpose interconnect since the direct and long line resources do not exhibit the same R-C delay accumulation. The Logic Cell Array is divided into nine sections with buffers automatically provided for general interconnect at the boundaries of these sections. These boundaries can be viewed with the development system. For routing within a section, no buffers are used. The delay calculator of the XACT development system automatically calculates and displays the block, interconnect and buffer delays for any selected paths.

Figure 7a. General-Purpose Interconnect

# Long Lines

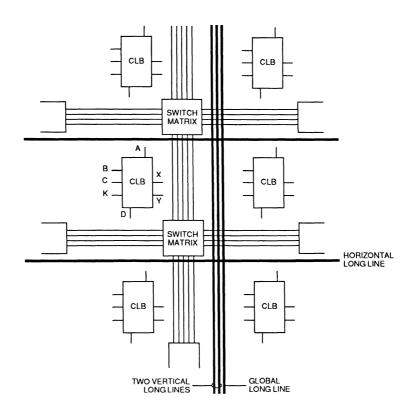

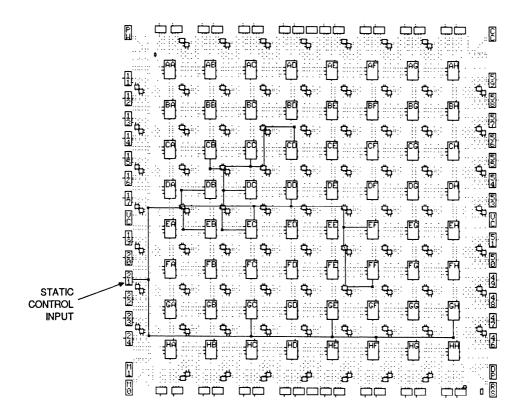

Long-lines, shown in Figure 8a, run both vertically and horizontally the height or width of the interconnect area. Each vertical interconnection column has two long lines; each horizontal row has one, with an additional long line adjacent to each set of I/O blocks. The long lines bypass the switch matrices and are intended primarily for signals that must travel a long distance or must have minimum skew among multiple destinations.

A global buffer in the Logic Cell Array is available to drive a single signal to all B and K inputs of logic blocks. Using the global buffer for a clock provides a very low skew, high fan-out synchronized clock for use at any or all of the logic blocks. At each block, a configuration bit for the K input to the block can select this global line as the storage element clock signal. Alternatively, other clock sources can be used.

A second buffer below the bottom row of the array drives a horizontal long line which, in turn, can drive a vertical long line in each interconnection column. This alternate buffer also has low skew and high fan-out capability. The network formed by this alternate buffer's long lines can be selected to drive the B, C or K inputs of the

0010003 7B

Figure 7b. Interconnection Switching Matrix

logic blocks. Alternatively, these long lines can be driven by a logic or I/O block on a column by column basis. This capability provides a common, low-skew clock or control line within each column of logic blocks. Interconnections of these long lines are shown in Figure 8b.

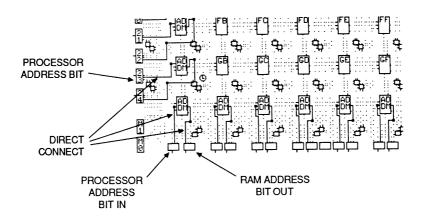

# **Direct Interconnect**

Direct interconnect, shown in Figure 9, provides the most efficient implementation of networks between adjacent logic or I/O blocks. Signals routed from block to block by means of direct interconnect exhibit minimum interconnect propagation and use minimum interconnect resources. For each Configurable Logic Block, the X output may be connected directly to the C or D inputs of the CLB above and to the A or B inputs of the CLB below it. The Y output can use direct interconnect to drive the B input of the block immediately to its right. Where logic blocks are adjacent to I/O blocks, direct connect is provided to the I/O block input (I) on the left edge of the die, the output (O) on the right edge, or

both on I/O blocks at the top and bottom of the die. Direct interconnections of I/O blocks with CLBs are shown in Figure 8b.

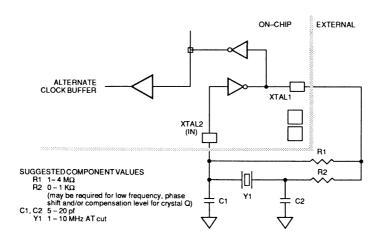

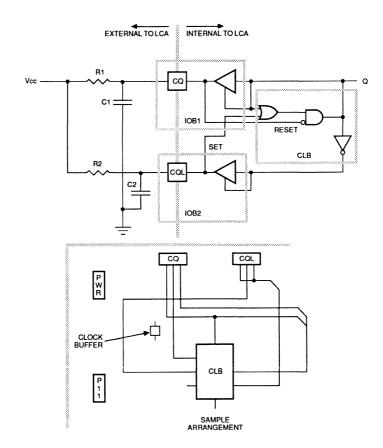

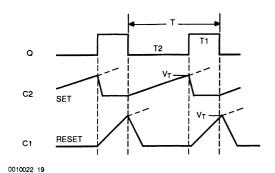

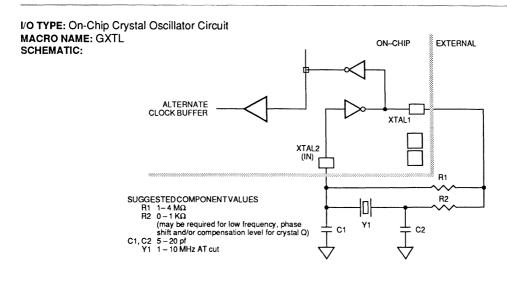

# Crystal Oscillator

An internal high speed inverting amplifier is available to implement an on-chip crystal oscillator. It is associated with the auxiliary clock buffer in the lower right corner of the die. When configured to drive the auxiliary clock buffer, two special adjacent user I/O blocks are also configured to connect the oscillator amplifier with external crystal oscillator components, as shown in Figure 10. This circuit becomes active before configuration is complete in order to allow the oscillator to stabilize. Actual internal connection is delayed until completion of configuration. The feedback resistor R1 between output and input, biases the amplifier at threshold. It should be as large a value as practical to minimize loading of the crystal. The inversion of the amplifier, together with the R-C networks and crystal, produce the 360-degree

Figure 8a. Long Line Interconnect

0010003 8A

0010003 8B

Figure 8b. XC2064 Long Lines, I/O Clocks, I/O Direct Interconnect

phase shift of the Pierce oscillator. A series resistor R2 may be included to add to the amplifier output impedance when needed for phase-shift control or crystal resistance matching or to limit the amplifier input swing to control clipping at large amplitudes. Excess feedback voltage may be adjusted by the ratio of C2/C1. The amplifier is designed to be used over the range from 1 MHz up to one-half the specified CLB toggle frequency. Use at frequencies below 1 MHz may require individual characterization with respect to a series resistance. Operation at frequencies above 20 MHz generally requires a crystal to operate in a third overtone mode, in which the fundamental frequency must be suppressed by the R-C networks. When the amplifier does not drive the auxiliary buffer, these I/O blocks and their package pins are available for general user I/O.

#### **POWER**

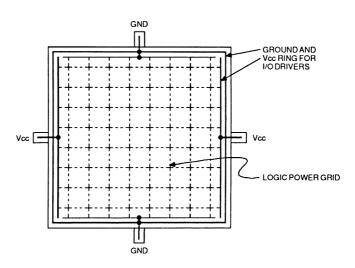

#### Power Distribution

Power for the LCA is distributed through a grid to achieve high noise immunity and isolation between logic and I/O. For packages having more than 48 pins, two

Figure 9. Direct Interconnect

Vcc pins and two ground pins are provided (see Figure 11). Inside the LCA, a dedicated Vcc and ground ring surrounding the logic array provides power to the I/O drivers. An independent matrix of Vcc and ground lines supplies the interior logic of the device. This power distribution grid provides a stable supply and ground for all internal logic, providing the external package power pins are appropriately decoupled. Typically a 0.1  $\mu\text{F}$  capacitor connected between the Vcc and ground pins near the package will provide adequate decoupling.

Output buffers capable of driving the specified 4 mA loads under worst-case conditions may be capable of driving 25 to 30 times that current in a best case. Noise can be reduced by minimizing external load capacitance and reducing simultaneous output transitions in the same direction. It may also be beneficial to locate heavily loaded output buffers near the ground pads. Multiple Vcc and ground pin connections are required for package types which provide them.

# **Power Dissipation**

The Logic Cell Array exhibits the low power consumption characteristic of CMOS ICs. Only quiescent power is required for the LCA configured for CMOS input levels. The TTL input level configuration option requires additional power for level shifting. The power required by the static memory cells which hold the configuration data is very low and may be maintained in a power-down mode.

Typically most of power dissipation is produced by capacitive loads on the output buffers, since the power per output is 25  $\mu W$  / pF / MHz . Another component of I/O power is the DC loading on each output pin. For any given system, the user can calculate the power requirement based on the resistive loading of the devices driven by the Logic Cell Array.

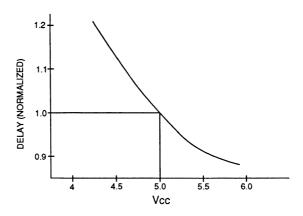

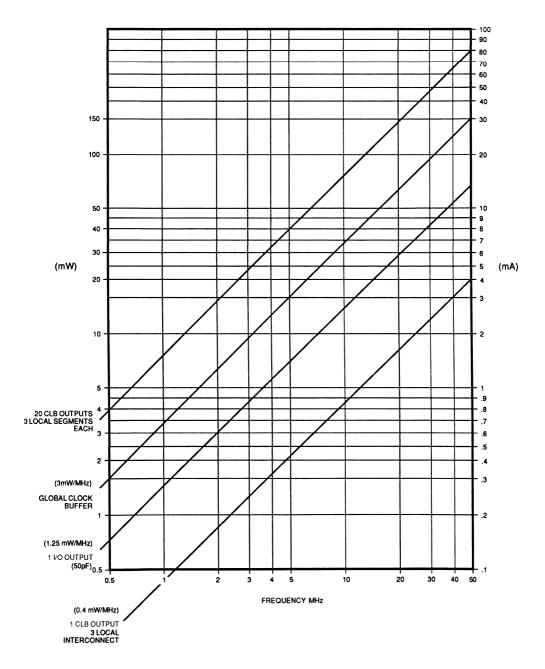

Internal power supply dissipation is a function of clock frequency and the number of nodes changing on each clock. In an LCA the fraction of nodes changing on a given clock is typically low (10–20%). For example, in a 16-bit binary counter, the average clock produces a change in slightly less than 2 of the 16 bits. In a 4-input AND gate there will be 2 transitions in 16 states. Typical global clock buffer power is about 3 mW / MHz for the XC2064 and 4mW / MHz for the XC2018. With a "typical" load of three general interconnect segments, each Configurable Logic Block output requires about 0.4 mW / MHz of its output frequency. Graphs of power versus operating frequency are shown in Table 1.

|  |         | XTAL1 | XTAL2 |

|--|---------|-------|-------|

|  | 48 DIP  | 33    | 30    |

|  | 68 PLCC | 46    | 43    |

|  | 68 PGA  | J10   | L10   |

|  | 84 PLCC | 56    | 53    |

|  | 84 PGA  | K11   | L11   |

0010003 10

Figure 10. Crystal Oscillator

0010003 11

Figure 11. LCA Power Distribution

#### **PROGRAMMING**

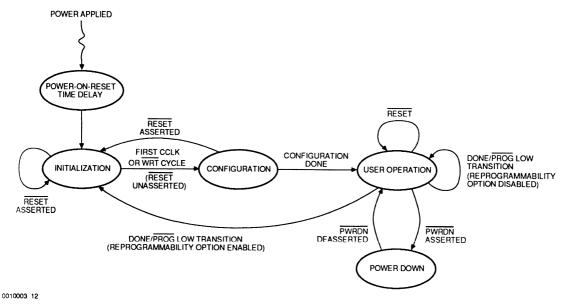

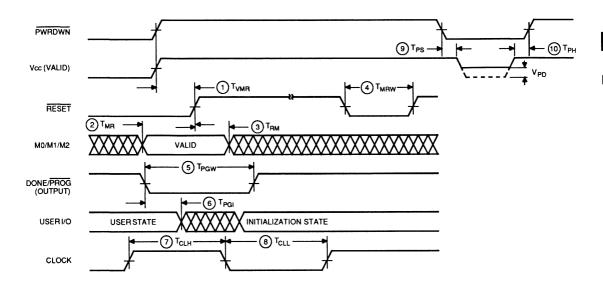

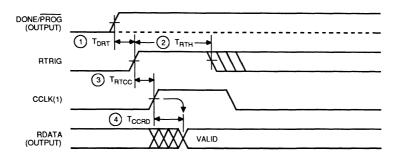

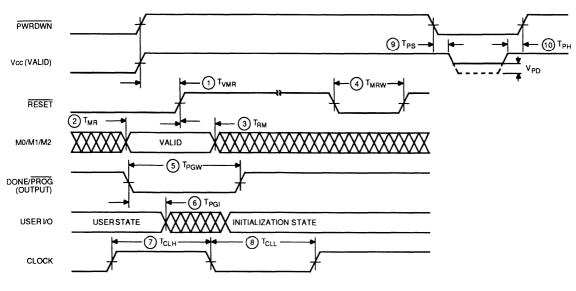

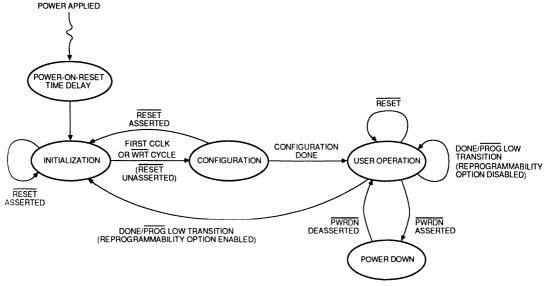

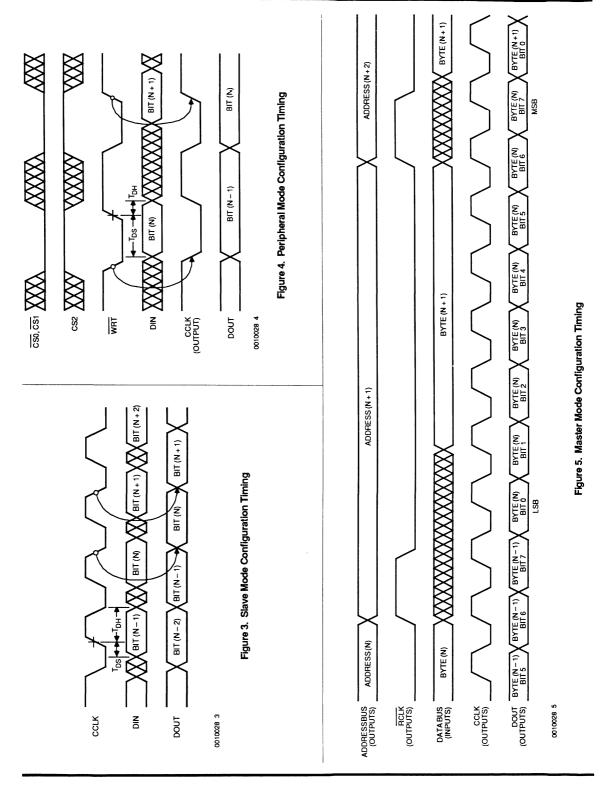

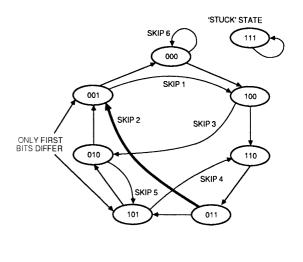

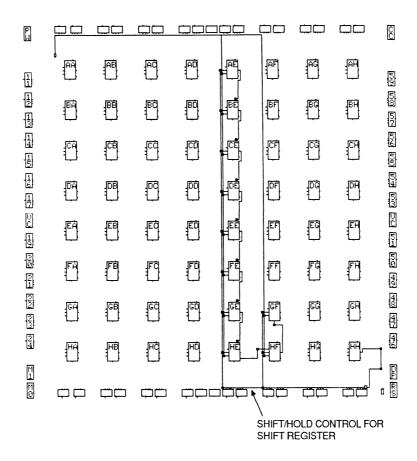

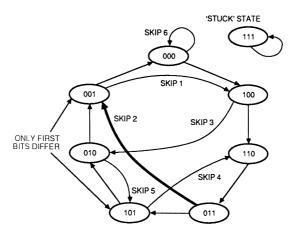

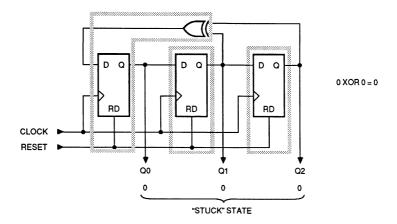

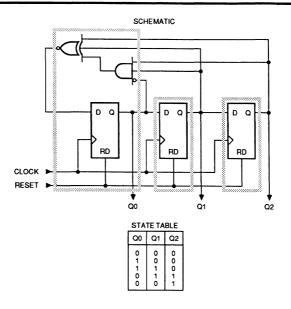

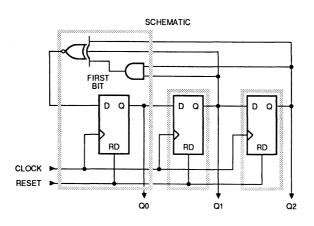

Configuration data to define the function and interconnection within a Logic Cell Array are loaded automatically at power-up or upon command. Several methods of automatically loading the required data are designed into the Logic Cell Array and are determined by logic levels applied to mode selection pins at configuration time. The form of the data may be either serial or parallel, depending on the configuration mode. The programming data are independent of the configuration mode selected. The state diagram of Figure 12 illustrates the configuration process.

Input thresholds for user I/O pins can be selected to be either TTL-compatible or CMOS-compatible. At power-up, all inputs are TTL-compatible and remain in that state until the LCA begins operation. If the user has selected CMOS compatibility, the input thresholds are changed to CMOS levels during configuration.

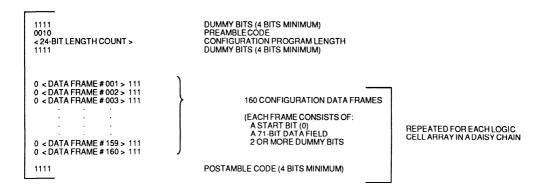

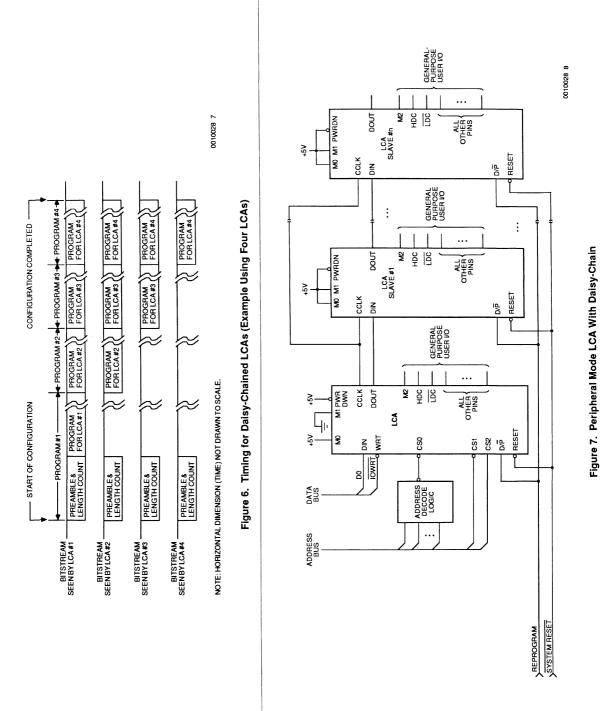

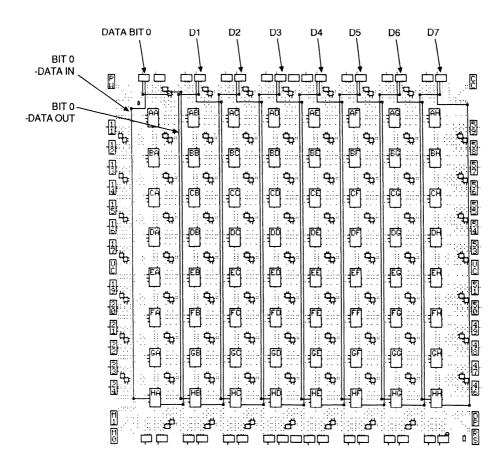

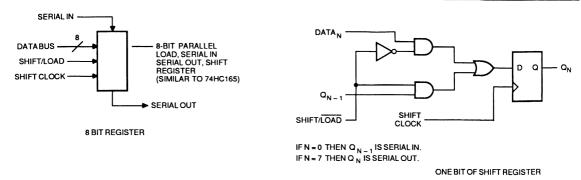

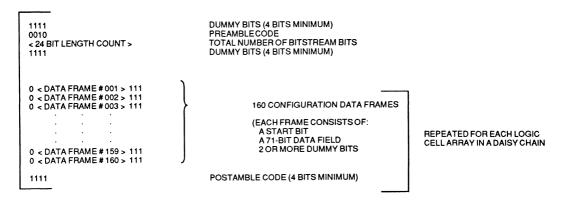

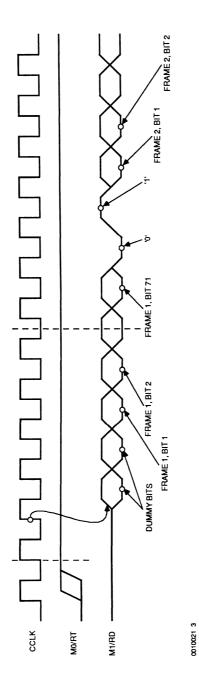

Figure 13 shows the specific data arrangement for the XC2064 device. Future products will use the same data format to maintain compatibility between different devices of the Xilinx product line, but they will have different sizes and numbers of data frames. For the XC2064, configuration requires 12,038 bits for each device. For the XC2018, the configuration of each device requires 17,878 bits. The XC2064 uses 160 configuration data frames and the XC2018 uses 197.

The configuration bit stream begins with preamble bits, a preamble code and a length count. The length count is loaded into the control logic of the Logic Cell Array and is used to determine the completion of the configuration process. When configuration is initiated, a 24-bit length counter is set to 0 and begins to count the total number of configuration clock cycles applied to the device. When the current length count equals the loaded length count, the configuration process is complete. Two clocks before completion, the internal logic becomes active and is reset. On the next clock, the inputs and outputs become active as configured and consideration should be given to avoid configuration signal contention. (Attention must be paid to avoid contention on pins which are used as inputs during configuration and become outputs in operation.) On the last configuration clock, the completion of configuration is signalled by the release of the DONE / PROG pin of the device as the device begins operation. This opendrain output can be AND-tied with multiple Logic Cell Arrays and used as an active-high READY or active-low, RESET, to other portions of the system. High during configuration (HDC) and low during configuration (LDC), are released one CCLK cycle before DONE is asserted. In master mode configurations, it is convenient to use LDC as an active-low EPROM chip enable.

As each data bit is supplied to the LCA, it is internally assembled into a data word. As each data word is completely assembled, it is loaded in parallel into one word of the internal configuration memory array. The last word must be loaded before the current length count compare is true. If the configuration data are in error, eg. PROM address lines swapped, the LCA will not be ready at the length count and the counter will cycle through an additional complete count prior to configuration being "done".

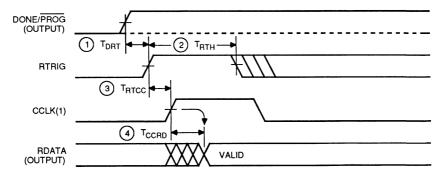

Figure 14 shows the selection of the configuration mode based on the state of the mode pins M0 and M1. These package pins are sampled prior to the start of the configuration process to determine the mode to be used. Once configuration is DONE and subsequent operation has begun, the mode pins may be used to perform data readback, as discussed later. An additional mode pin, M2, must be defined at the start of configuration. This package pin is a user-configurable I/O after configuration is complete.

#### Initialization Phase

When power is applied, an internal power-on-reset circuit is triggered. When Vcc reaches the voltage at which the LCA begins to operate (2.5 to 3 Volts), the chip is initialized, outputs are made high-impedance and a time-out is initiated to allow time for power to stabilize. This time-out (15 to 35 ms) is determined by a counter driven by a self-generated, internal sampling clock that drives the configuration clock (CCLK) in master configuration mode. This internal sampling clock will vary with process, temperature and power supply over the range of 0.5 to 1.5 MHz. LCAs with mode lines set for master mode will time-out of their initialization using a longer counter (60 to 140 ms) to assure that all devices, which it may be driving in a daisy chain, will be ready. Con-

| М  | DDE P | NIV. | MODE SELECTED    | 0010003 1 |

|----|-------|------|------------------|-----------|

| МО | M1    | M2   | MODE SEEEOTED    |           |

| 0  | 0     | 0    | MASTERSERIAL     |           |

| 0  | 0     | 1    | MASTER LOW MODE  |           |

| 0  | 1     | 1    | MASTER HIGH MODE |           |

| 1  | 0     | 1    | PERIPHERALMODE   |           |

| 1  | 1     | 1    | SLAVEMODE        |           |

MASTER LOW ADDRESSES BEGIN AT 0000 AND INCREMENT MASTER HIGH ADDRESSES BEGIN AT FFFF AND DECREMENT

Figure 14. Configuration Mode Selection

figuration using peripheral or slave modes must be delayed long enough for this initialization to be completed.

The initialization phase may be extended by asserting the active-low external RESET. If a configuration has begun, an assertion of RESET will initiate an abort, including an orderly clearing of partially loaded configuration memory bits. After about 3 clock cycles for synchronization, initialization will require about 160 addi-

tional cycles of the internal sampling clock (197 for the XC2018) to clear the internal memory before another configuration may begin. The same is true of a configured part in which the reconfigurable control bit is set. When a HIGH-to-LOW transition on the DONE / PROG package pin is detected, thereby initiating a reprogram, the configuration memory is cleared. This insures an orderly configuration in which no internal signal conflicts are generated during the loading process.

Figure 12. Configuration State Diagram

0010003 13

Figure 13. XC2064 Configuration Data Arrangement

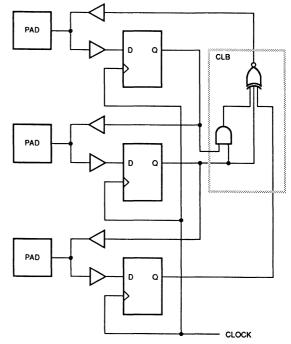

#### **Master Mode**

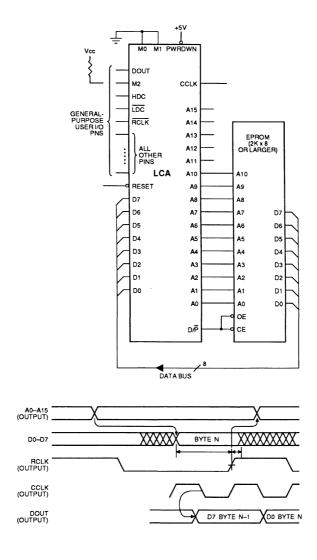

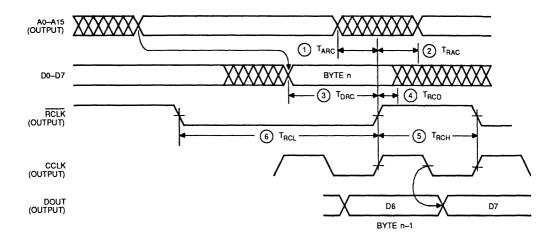

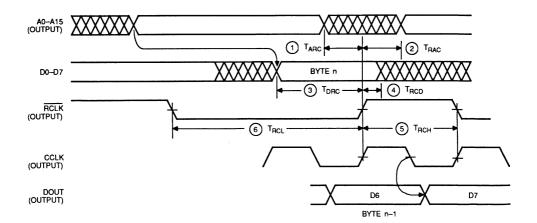

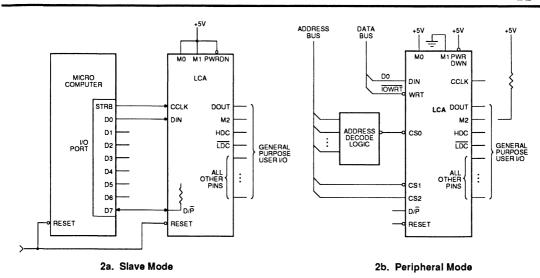

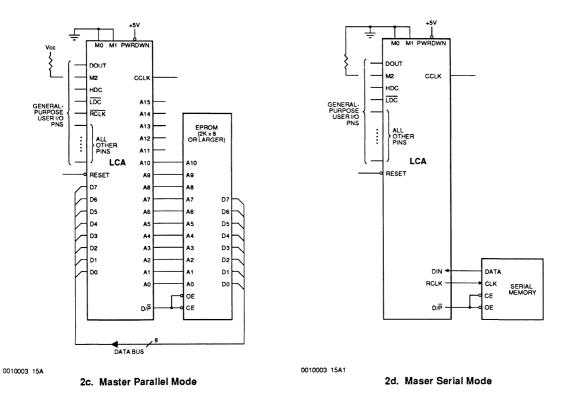

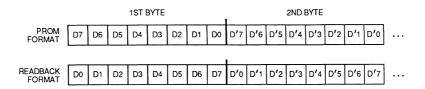

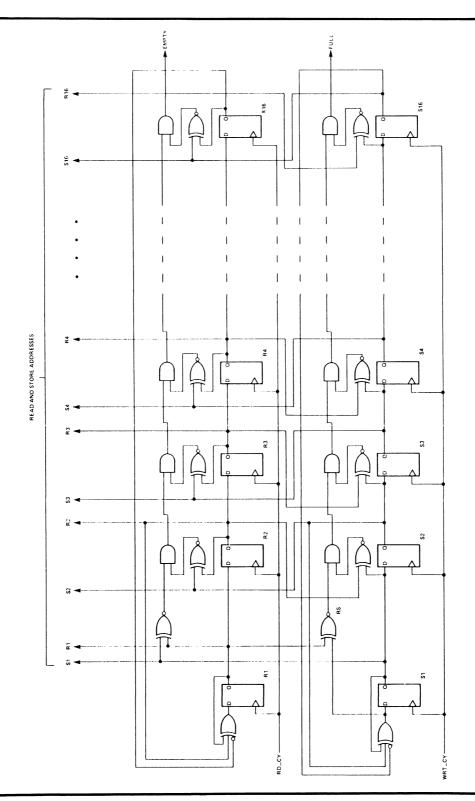

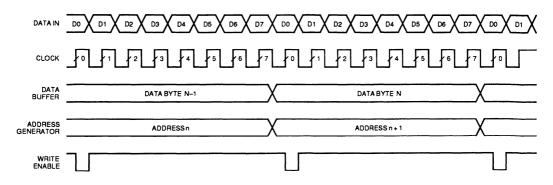

In master mode, the Logic Cell Array automatically loads the configuration program from an external memory device. Figure 15a shows an example of the master mode connections required. The Logic Cell Array provides sixteen address outputs and the control signals RCLK (read clock), HDC (high during configuration) and LDC (low during configuration) to execute read cycles from the external memory. Parallel eight-bit data words are read and internally serialized. As each data word is

read, the least significant bit of each byte, normally D0, is the next bit in the serial stream.

Addresses supplied by the Logic Cell Array can be selected by the mode lines to begin at address 0 and incremented to read the memory (master low mode), or they can begin at address FFFF Hex and be decremented (master high mode). This capability is provided to allow the Logic Cell Array to share external memory with another device, such as a microprocessor. For example, if the processor begins its execution from

Figure 15a. Master Low Address Configuration

0010003 15A

low memory, the Logic Cell Array can load itself from high memory and enable the processor to begin execution once configuration is completed. The DONE / PROG output pin can be used to hold the processor in a Reset state until the Logic Cell Array has completed the configuration process.

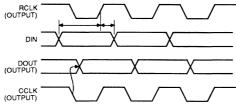

The master serial mode uses serial configuration data, synchronized by the rising edge of RCLK, as in Figure 15b.

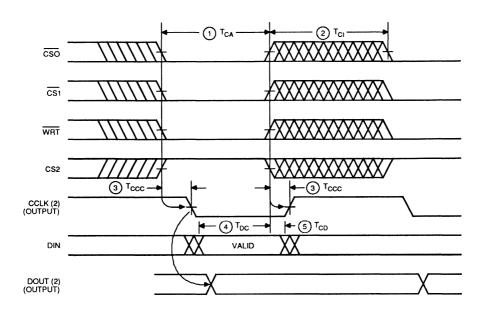

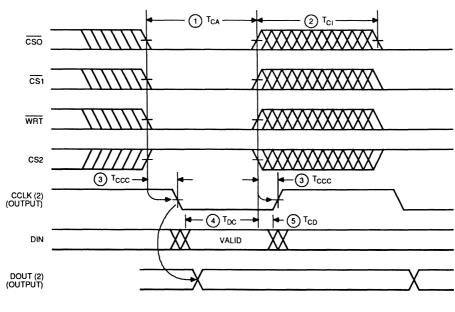

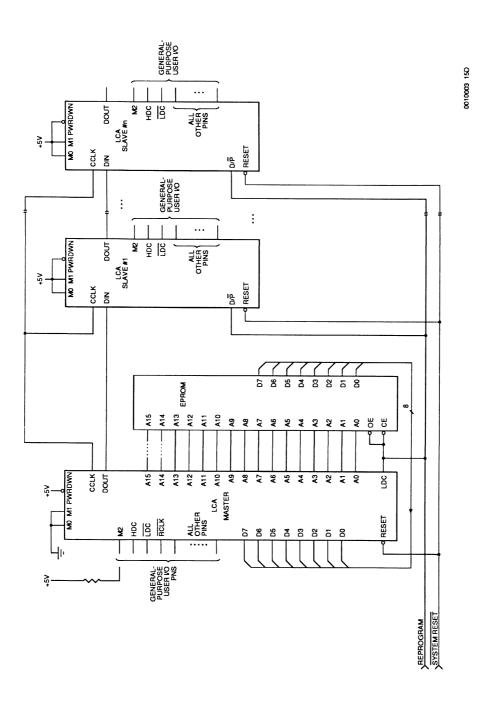

# **Peripheral Mode**

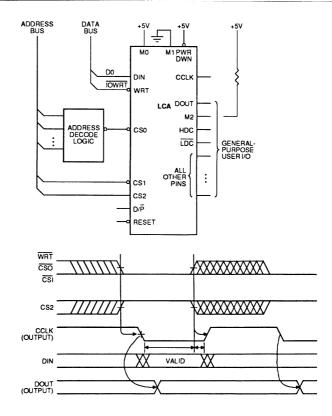

Peripheral mode provides a simplified interface through which the device may be loaded as a processor

peripheral. Figure 16 shows the peripheral mode connections. Processor write cycles are decoded from the common assertion of the active-low write strobe (WRT), and two active-low and one active-high chip selects (CS0 CS1 CS2). If all these signals are not available, the unused inputs should be driven to their respective active levels. The Logic Cell Array will accept one bit of the configuration program on the data input (DIN) pin for each processor write cycle. Data is supplied in the serial sequence described earlier.

Since only a single bit from the processor data bus is loaded per cycle, the loading process involves the processor reading a byte or word of data, writing a bit of the data to the Logic Cell Array, shifting the word and

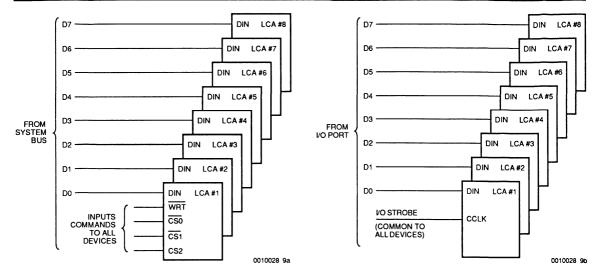

0010003 15A1

Figure 15b. Master Serial Mode Configuration

writing a bit until all bits of the word are written, then continuing in the same fashion with the next word, etc. After the configuration program has been loaded, an additional three clocks (a total of three more than the length count) must be supplied in order to complete the configuration process. When more than one device is being used in the system, each device can be assigned a different bit in the processor data bus, and multiple devices can be loaded on each processor write cycle. This "broadside" loading method provides a very easy and time-efficient method of loading several devices.

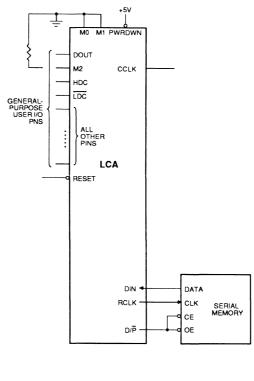

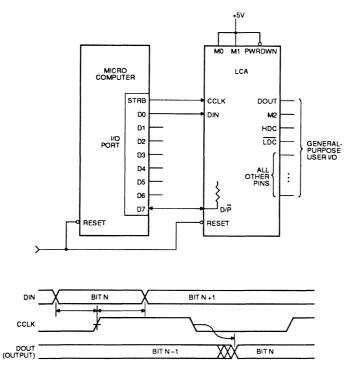

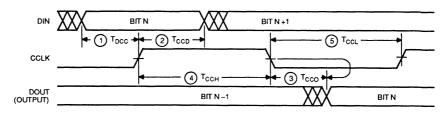

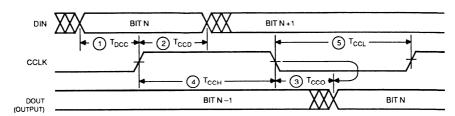

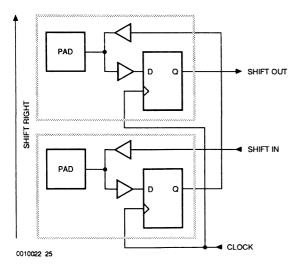

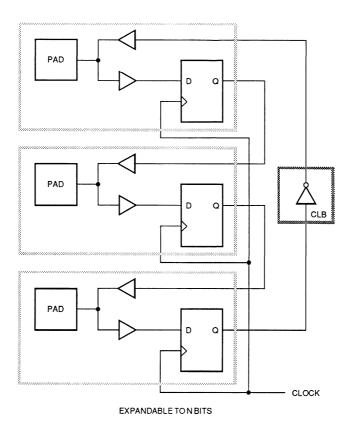

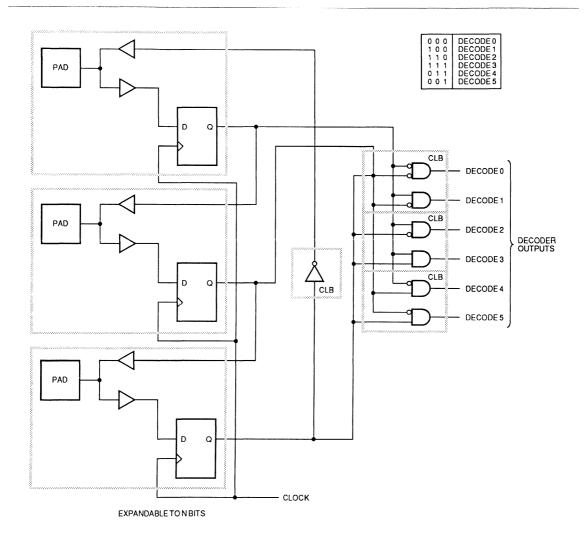

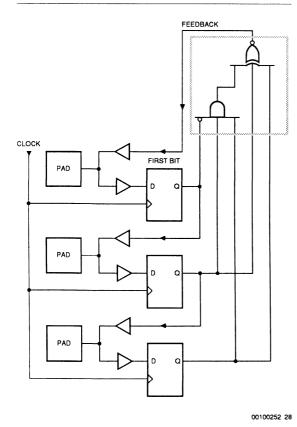

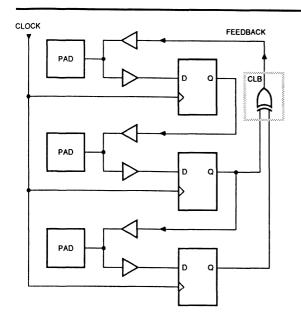

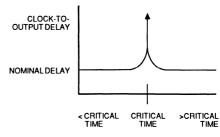

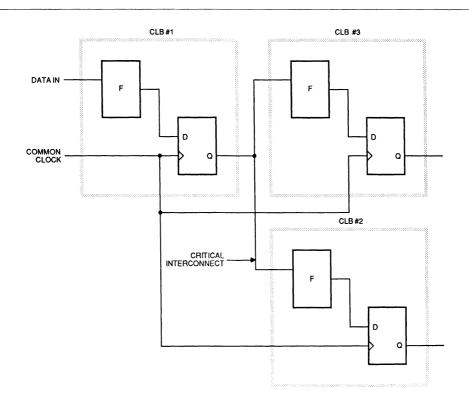

#### Slave Mode

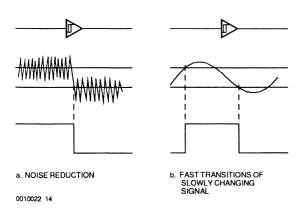

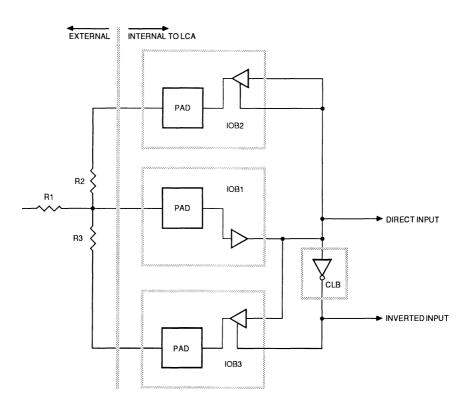

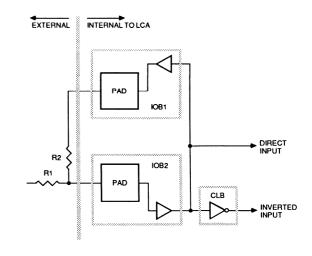

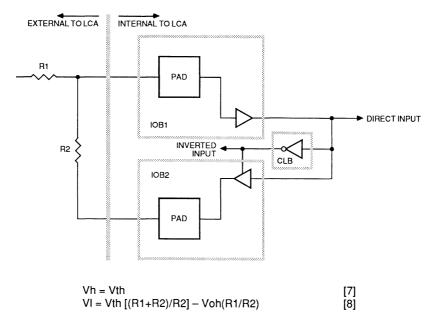

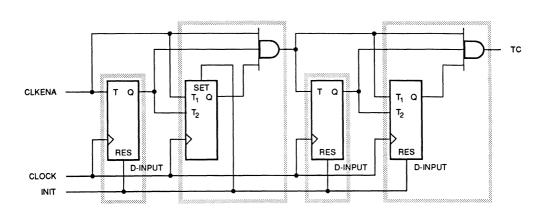

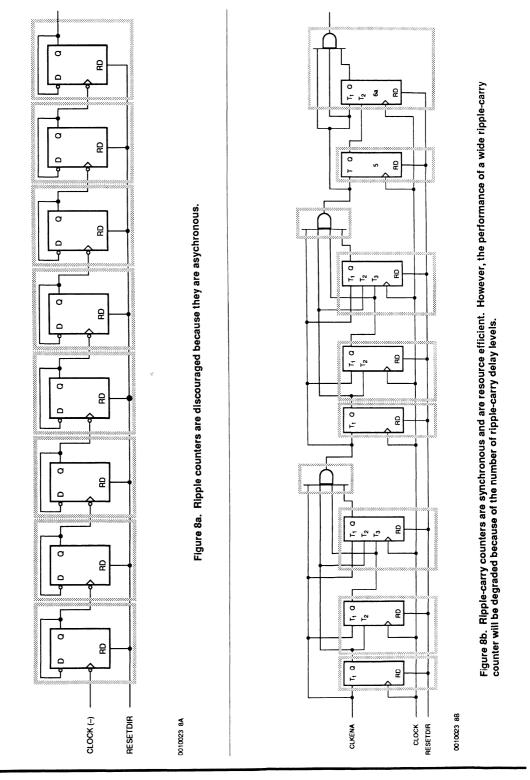

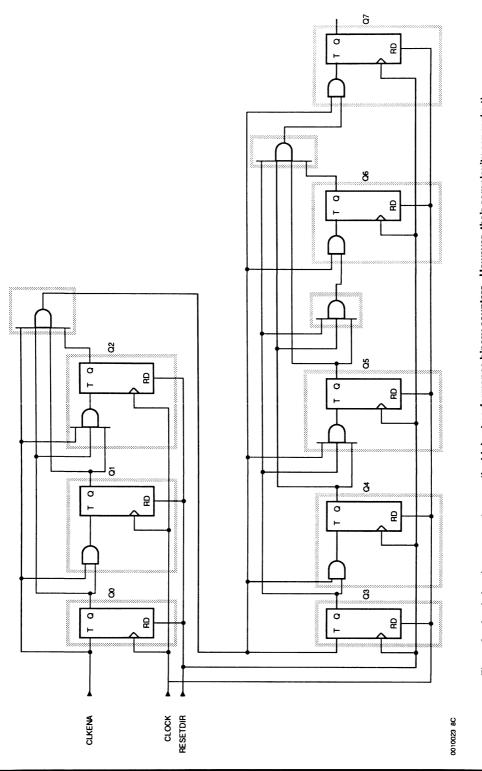

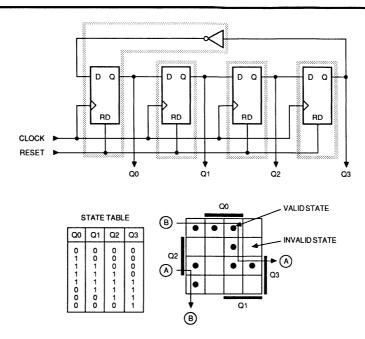

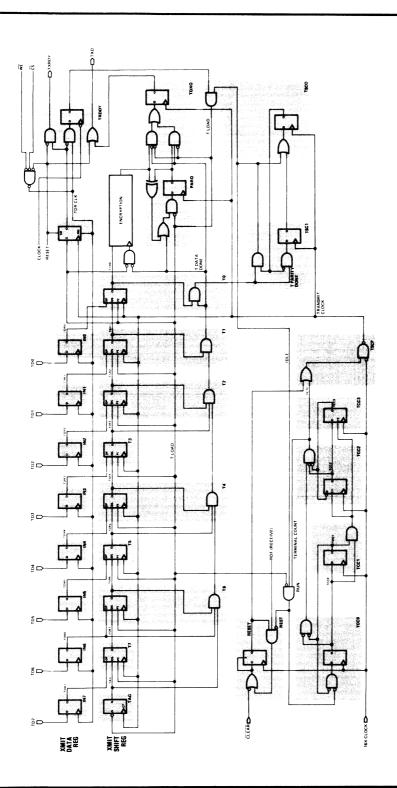

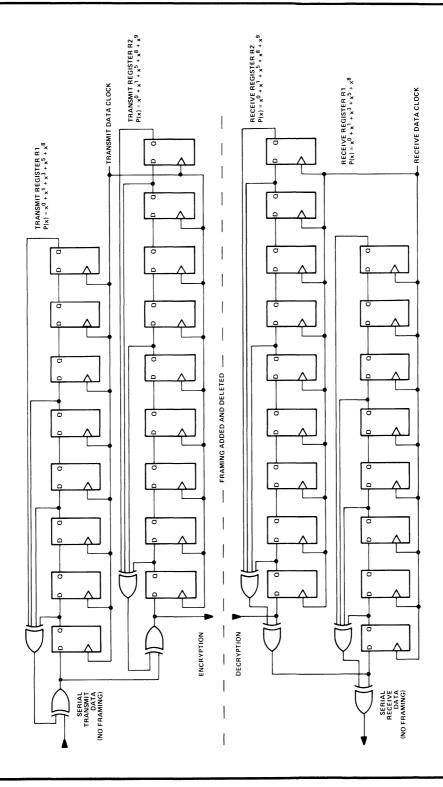

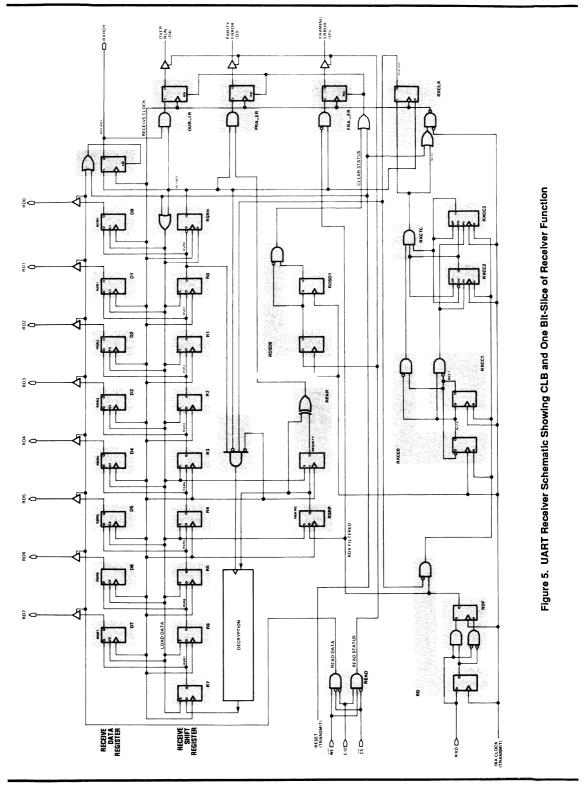

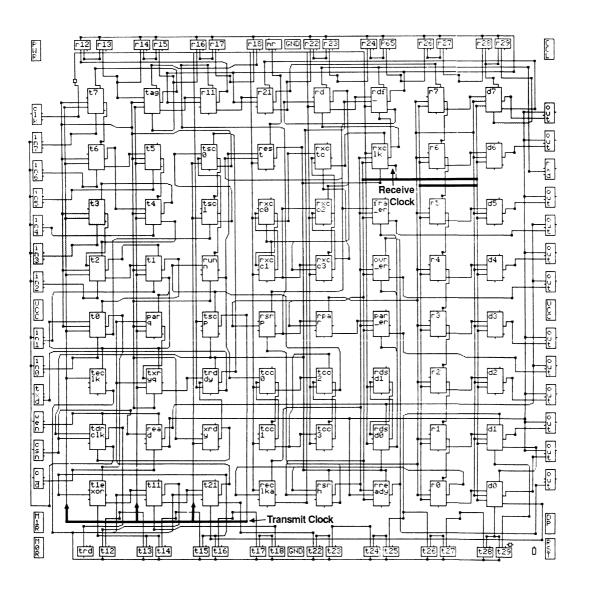

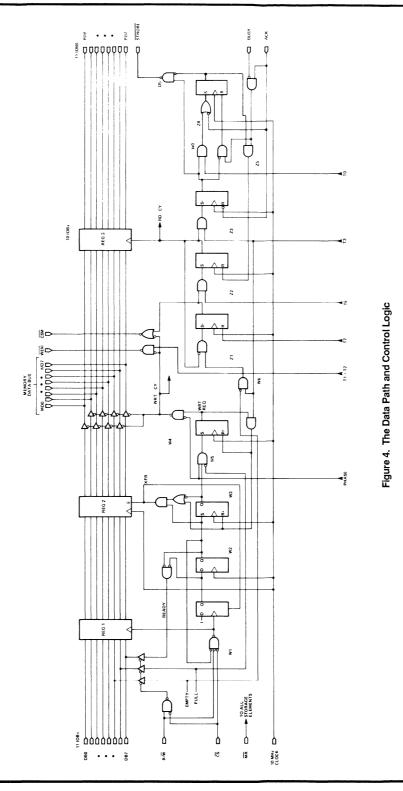

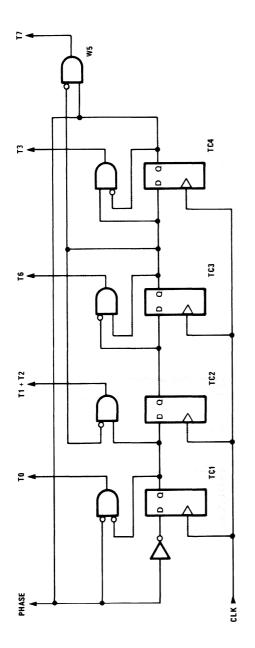

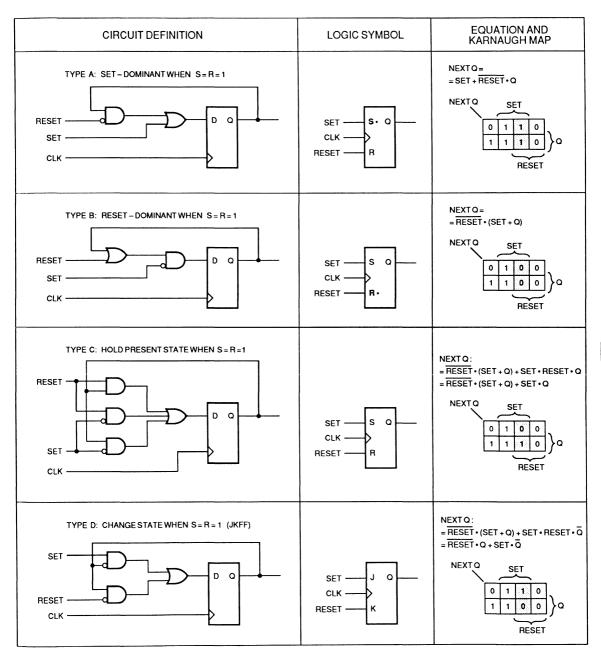

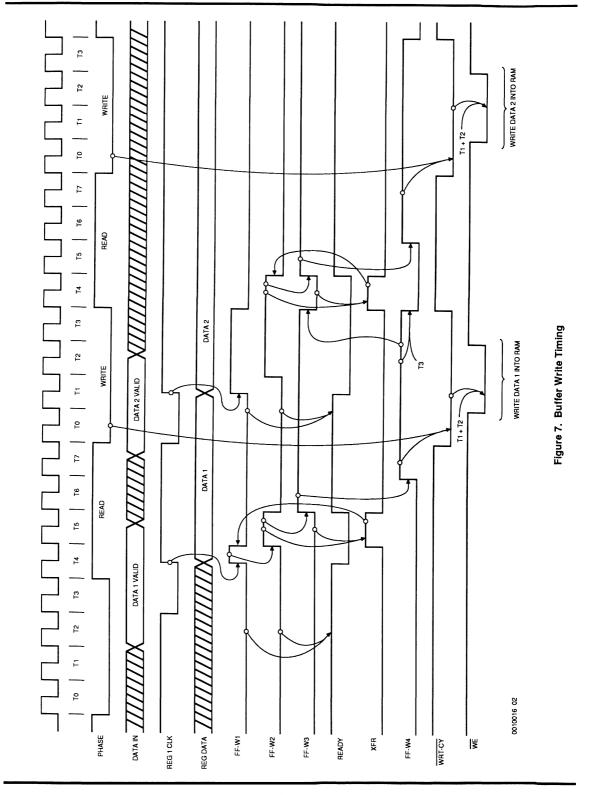

Slave mode, Figure 17, provides the simplest interface for loading the Logic Cell Array configuration. Data is supplied in conjunction with a synchronizing clock. For each LOW-to-HIGH input transition of configuration clock (CCLK), the data present on the data input (DIN) pin is loaded into the internal shift register. Data may be supplied by a processor or by other special circuits. Slave mode is used for downstream devices in a daisychain configuration. The data for each slave LCA are supplied by the preceding LCA in the chain, and the